# An Instruction Set Extension to Support Software-Based Masking

Si Gao<sup>1</sup>, Johann Großschädl<sup>2</sup>, Ben Marshall<sup>3,6</sup>, Dan Page<sup>3</sup>, Thinh Pham<sup>3</sup> and Francesco Regazzoni<sup>4,5</sup>

<sup>1</sup> Alpen-Adria Universität Klagenfurt, Klagenfurt, Austria. si.gao@aau.at

<sup>2</sup> Department of Computer Science, University of Luxembourg, Luxembourg, Luxembourg. johann.groszschaedl@uni.lu

<sup>3</sup> Department of Computer Science, University of Bristol, Bristol, UK. {ben.marshall,daniel.page,th.pham}@bristol.ac.uk

<sup>4</sup> University of Amsterdam, Amsterdam, The Netherlands f.regazzoni@uva.nl

<sup>5</sup> UniversitÄă della Svizzera italiana, Lugano, Switzerland francesco.regazzoni@usi.ch

<sup>6</sup> PQShield Ltd, Oxford, UK. ben.marshall@pqshield.com

**Abstract.** In both hardware and software, masking can represent an effective means of hardening an implementation against side-channel attack vectors such as Differential Power Analysis (DPA). Focusing on software, however, the use of masking can present various challenges: specifically, it often 1) requires significant effort to translate any theoretical security properties into practice, and, even then, 2) imposes a significant overhead in terms of efficiency. To address both challenges, this paper explores the use of an Instruction Set Extension (ISE) to support masking in software-based implementations of a range of (symmetric) cryptographic kernels including AES: we design, implement, and evaluate such an ISE, using RISC-V as the base ISA. Our ISE-supported first-order masked implementation of AES, for example, is an order of magnitude more efficient than a software-only alternative with respect to both execution latency and memory footprint; this renders it comparable to an unmasked implementation using the same metrics, but also first-order secure.

Keywords: side-channel attack, masking, RISC-V, ISE

# 1 Introduction

The threat of implementation attacks. Evolution of the technology landscape, for example improvement in storage, computational, and communication capability, has produced a corresponding evolution in user-facing platforms and applications that we now routinely depend on. Many such cases are now deemed security-critical, as a result of trends such increased connectivity (cf. IoT), outsourced computation (cf. cloud computing), and use of identity-, location-, and finance-related data. Within this setting, cryptography often represents a transparent enabler: cryptographic solutions are routinely tasked with ensuring the secrecy, robustness, and provenience of our data (when communicated and/or while stored), plus the authenticity of interacting parties. While mature theoretical foundations often underpin such solutions, their secure realisation in practice can remain difficult. Cryptographic implementations represent an important component of the attack surface;

in an attack landscape of increasing breadth and complexity (where "attacks only get better"), the threat of implementation attacks is particularly acute.

The premise of an implementation attack is that by considering a concrete implementation, versus an abstract specification say, theoretical security properties (however strong) can potentially be bypassed. At a high level, they are often divided into active (e.g., fault injection) or passive (i.e., side-channel) classes. Differential Power Analysis (DPA) [KJJ99, MOP07] is a concrete example<sup>1</sup> of a side-channel attack with particular relevance to embedded devices. Following an optional profiling phase, a typical DPA attack performs an initial, online acquisition phase: (passive) monitoring by the attacker yields traces of power consumption during computation of some target operation by the target device. The underlying assumption is that *both* operations (e.g., addition versus multiplication) *and* the operands they process (e.g., higher versus lower Hamming weight) contribute to features, or leak information, then evident in the traces. Such features are harnessed by a subsequent, offline analysis phase, which attempts to recover security-critical information (e.g., key material) they relate to.

**Challenges in realisation of countermeasures.** Techniques for mitigating implementation attacks are becoming increasingly well understood. At a high level, examples pertinent to DPA are often classified as based on hiding [MOP07, Chapter 7] and/or masking [MOP07, Chapter 10]. The latter, which is our focus, can be viewed as a lower-level analogy of the more typically higher level "computing on encrypted data" concept. For a target operation normally invoked as r = f(x), application of a given masking scheme demands that 1) x is masked (resp. encrypted) to yield  $\tilde{x}$ , 2) alternative computation is applied to  $\tilde{x}$ , i.e.,  $\tilde{r} = \tilde{f}(\tilde{x})$ , such that it acts on the *underlying* x in a manner compatible with f, then 3)  $\tilde{r}$  is unmasked (resp. decrypted) to yield r; any leakage stemming from the computation of  $\tilde{f}$  will now relate to  $\tilde{x}$  rather than x, so the latter cannot be directly recovered as would likely be the case using f.

In common with other countermeasures, masking can be utilised at various levels in either hardware and/or software: for example, algorithm-level (e.g., to a block cipher such as AES [Mes01]), system-level (e.g., across the datapath of a processor core [GJM<sup>+</sup>16, MGH19]), and gate-level (e.g., in secure logic style such as MDPL [PM05]) techniques are all viable. For a concrete implementation that uses such techniques, however, at least two significant challenges must be addressed. First, it must translate theoretically modelled security properties into practice. This challenge is neatly illustrated by the contrast between a theoretically, *provably* secure masking scheme proposed by Rivain and Prouff [RP10], versus attacks on a practical implementation thereof by Balasch et al. [BGG<sup>+</sup>14]. Second, it must do so while satisfying other quality metrics such as demand for high-volume, low-latency, high-throughput, low-footprint, and/or low-power.

**An ISE-assisted approach to masking.** Instruction Set Extensions (ISEs) [GB11, BGM09, RI16] have proved to be an effective implementation technique within the context of cryptography. The idea is to identify, e.g., through benchmarking, a set of additional instructions that allow the target operation to leverage special-purpose, domain-specific functionality in the resulting ISE, versus general-purpose functionality in the base Instruction Set Architecture (ISA), and thereby deliver improvement with respect to pertinent quality metrics. ISEs are *particularly* effective for embedded devices, because they afford a compromise improving footprint and latency versus a software-only option while also improving area and flexibility versus a hardware-only option.

There is an increasingly accepted argument (see, e.g., [RKL<sup>+</sup>04, RRKH04, BMT16]) that security should be considered as a first-class metric at design-time, rather than a

$<sup>^{1}</sup>$ Although our focus is specifically on DPA, we note that associated attack and countermeasure techniques apply more generally, e.g., to classes such as EM.

problem to be addressed in a reactive, post hoc manner. In line with such an argument, this paper explores use of an ISE as a means of supporting masking in software-based implementations of cryptography: we design, implement, and evaluate such an ISE using RISC-V as the base ISA. We suggest there are (at least) three reasons an ISE-based approach may be attractive versus alternatives (e.g., a dedicated IP module). First, use of masking in software-only implementations will impose a significant overhead, e.g., with respect to execution latency and demand for high-quality randomness; our ISE can help mitigate this problem. Second, an ISE is well positioned to act as an interface with respect to security properties. For example, there is increased evidence (see, e.g., [CGD18, GMPO19]) that secure use of masking in software-only implementations is complicated by the lack of guarantees regarding leakage that stems from the underlying micro-architecture; our ISE can help mitigate this problem, e.g., by adopting an approach similar to the augmented ISA (or aISA) of Ge et al. [GYH18] and constraining the micro-architecture to meet properties demanded by the ISA. Third, the design of masking schemes is a relatively fast-paced field, with novel designs and techniques appearing regularly. Our ISE mitigates this problem by following a RISC-like ethos: it provides a suite of general-purpose "building block" operations, that can be used to support a wide range of cryptographic constructions (e.g., block ciphers) and higher-level masking schemes.

We note that, concurrently with our work, Kiaei and Schaumont [KS20] published a proposal that is similar in some respects. We detail the differences between their and our work in Section 2.3, but, in short, we a) enrich the ISE with a wider set of operations, b) provide an implementation of the ISE within an existing RISC-V compliant micro-architecture, and c) evaluate it, with respect to efficiency and security properties, using a suite of representative kernels.

**Organisation.** Section 2 surveys related work. Section 3 introduces the ISE design. Section 4 looks at the ISE from a hardware perspective, outlining and then evaluating an implementation of the ISE set within the context of an existing RISC-V compliant micro-architecture. Section 5 looks at the ISE from a software perspective, focusing on how it is utilised: we evaluate the ISE when used to implement a range of (symmetric) cryptographic kernels including AES. Finally, Section 6 concludes our work presenting potential directions for future work.

# 2 Background

### 2.1 RISC-V

RISC-V (see, e.g., [AP14, Wat16]) is an open ISA specification. It adopts *strongly* RISCoriented design principles (so is similar to MIPS) and can be implemented, modified, or extended by anyone with neither licence nor royalty requirements (as opposite to MIPS, ARM, and x86). A central tenet of the ISA is modularity: a general-purpose base ISA can be augmented with some set of special-purpose, standard or non-standard (i.e., custom) extensions. As a result of these features, coupled with the surrounding community and availability of supporting infrastructure such as compilation tool-chains, a range of (typically open-source) RISC-V implementations exist.

We focus without loss of generality on extending RV32I [RV:19, Section 2], i.e., the 32-bit integer RISC-V base ISA. Let GPR[i], for  $0 \le i < 32$ , denote the *i*-th entry of the general-purpose register file. RISC-V uses XLEN to denote the word size; we adopt the same approach, but by focusing on RV32I assume a focus on XLEN = 32.

### 2.2 Masking

Masking is based on the concept of secret-sharing. In 1999, Chari et al. [CJRR99] leveraged this concept as a countermeasure against side-channel attacks. However, use of the term masking first appeared in 2000 when Messerges [Mes01] described the use of a "random mask to obscure the calculation made by the fundamental operations" of AES candidates.

A given masking scheme specifies a non-standard *representation* of data, where each variable x is represented by (or split into) n separate shares, and a non-standard *implementation* of functions, which operate on said representations. The shares representing some x must fulfil two properties: 1) they must be uniformly distributed, and 2) every subset of shares has to be statistically independent from x. An implementation of such a scheme is said to resist a t-th order attack (e.g., under the probing model of Ishai, Sahai, and Wagner [ISW03]), if knowledge of t < n shares cannot be used to recover x.

#### 2.2.1 Representation

A masking scheme can be classified as Boolean (or additive) or arithmetic (or multiplicative). If  $x_i$  denotes the *i*-th share for  $0 \le i < n$ , the shares representing x satisfy  $x_0 \oplus x_1 \oplus \cdots \oplus x_{n-1}$ under Boolean masking, and  $x_0 + x_1 + \cdots + x_{n-1} \pmod{2^w}$  under arithmetic masking. Consider the specific case of n = 2, and let  $\hat{x} = (x_0, x_1)$  denote the representation of some x under Boolean masking, i.e., as two shares  $x_0$  and  $x_1$ : this demands  $x = x_0 \oplus x_1$ . Likewise, let  $\bar{x} = (x_0, x_1)$  denote the representation of some x under arithmetic masking: this demands  $x = x_0 + x_1 \pmod{2^w}$ , noting that, without loss of generality, we set w = XLEN = 32.

#### 2.2.2 Hardware-oriented implementation

**Classical.** Goubin and Patarin [GP99] formalised the idea of replacing each intermediate variable of the computation that is dependent of the inputs or outputs (thus potentially exploitable by an attacker), by a combination of sub-variables. The recovery of the original variable would be possible only when all the sub-variables are combined together. This approach is secure if the function selected for implementing the combination operation allows one to perform computation with the sub-variables without computing the original variable. The two functions analysed are XOR (cf. additive masking) and modular multiplication (cf. multiplicative masking).

**Threshold Implementation (TI).** Threshold Implementation (TI), presented by Nikova et al. [NRR06], is a countermeasure that is provable secure against first-order attacks (even in the presence of glitches). TI requires use of shares with three properties: correctness, incompleteness, and uniformity. Correctness means that the computation performed on the shares should be correct, i.e., composition of the results of the operations carried out on each shares has to be equal to the shared representation of the original result. Incompleteness means that the computation performed is independent of at least one share (for first-order security). To guarantee the security of the scheme, masks must be uniformly distributed. Uniformity is usually the most difficult property to guarantee, but can be relaxed by using non-uniform functions *if* their randomness is refreshed frequently.

**Domain-Oriented Masking (DOM).** Domain-Oriented Masking (DOM) is presented by Gross et al. [GMK16]. The main objective of their work was to guarantee security against *t*-th order attacks using n = t + 1 shares, reaching the same level of security of TI, but incurring in less area overhead (when implemented in hardware) and requiring less randomness. To achieve this, the authors concentrate their effort in the design of the DOM-dep multiplier, that is a dedicated masked multiplier implementing the proposed scheme in an efficient and secure way. The approach is evaluated using the AES algorithm as a case of study, which is analysed up to a 15-th order security level.

#### 2.2.3 Software-oriented implementation

Although masking can be applied to more general classes of computation, consider application to block ciphers specifically. The main challenge when applying masking in software is to implement the round functions in such a way that the shares can be processed independently from each other, while it still must be possible to recombine them at the end of the execution to get the correct result. This is fairly easy for all linear operations, but can introduce massive overheads for the non-linear parts of a block cipher, e.g., S-boxes or modular additions/subtractions. Furthermore, all round transformations need to be executed twice (namely for  $x_0$  and  $x_1$ , where  $x = x_0 \oplus x_1$ ), which imposes additional overhead. Another problem is that a basic 2-share masking scheme is vulnerable to a so-called second-order attack where an attacker combines information from two leakage points. Such a second-order attack can, in turn, be thwarted by second-order masking, in which each sensitive variable is concealed with two random masks and, consequently, represented by three shares.

Depending on the algorithmic properties of a block cipher, a masking scheme can have to protect Boolean operations (e.g., XOR, shift) or arithmetic operations (e.g., modular addition). When a block cipher involves both Boolean and arithmetic operations, it is necessary to convert the masks from one form to the other to obtain the correct ciphertext (or plaintext). Examples of symmetric algorithms that involve arithmetic as well as Boolean operations include the widely-used hash functions SHA-2, Blake, and Skein, and any ARX-based block cipher (e.g., Speck). In essence, the basic operations performed by common block ciphers can be divided into three categories depending on how costly they are to mask in software: 1) linear operations (e.g., XOR, NOT, shift, rotation), 2) non-linear Boolean operations (e.g., AND, OR), and 3) non-linear arithmetic operations (e.g., modular addition, and inversion in  $\mathbb{F}_{2^8}$ ).

As mentioned before, linear operations like XOR and rotation are fairly easy to mask in software since one just has to apply the operation to each pair of shares individually. The XOR of a constant to a set of shares can be performed by XOR'ing it to a single share. Similarly, the logical NOT operation is masked by applying NOT to one of the shares. Computing a non-linear Boolean function on the shares assuring all variables processed are independent of sensitive variables is more complicated and introduces higher computational overheads. The simplest non-linear Boolean operations is the logical AND, which can be masked in different ways, whereby the different approaches proposed in the literature differ by the amount or randomness and the number of underlying basic operations. The first proposal for a first-order masked AND gate came from Trichina and was published more than 15 years ago [Tri03]. This so-called "Trichina AND-gate" consists of four basic AND operations, four XORs, and requires additional fresh randomness to ensure that the shares are statistically independent of any sensitive variable. Biryukov et al. introduced an improved expression for masked AND in [BDCU17], that consists of only seven basic operations and does not require an additional random variable since the shares are inherently refreshed. Furthermore, on ARM micro-controllers, the masked AND can be performed using only six basic instructions. Biryukov et al. also presented a masked OR operation, which consists of only six basic operations (and six basic instructions on ARM) and does not require fresh randomness.

Highly non-linear arithmetic operations, such as modular addition or inversion in a binary field, are the most costly operations when it comes to masking in software. There are two basic options for implementing a masked addition (or subtraction) in software; the first consists of converting the Boolean shares to arithmetic shares, then performing the addition on the arithmetic shares, and finally converting the arithmetic shares of the sum back to Boolean shares. The second option is to perform the modular addition directly on Boolean shares without conversion. Both options have in common that a straightforward software implementation has a complexity that increases linearly with the length of the operands to be added. Coron et al. presented in [CGTV15] a recursive formula for arithmetic addition on Boolean shares with logarithmic complexity. This approach is based on the Kogge-Stone adder (a special variant of a carry-lookahead adder) and uses masked AND, masked XOR, and masked shift as sub-operations. Biryukov et al. presented an improved Kogge-Stone adder that uses the more efficient masked operations from [BDCU17] and is able to perform a 32-bit addition on Boolean shares between 14% and 19% faster than the Kogge-Stone adder of Coron et al.

#### 2.3 Related work

Gross et al.  $[GJM^+16]$  propose a SCA-protected processor design based on the open-source V-scale RISC-V processor. The starting point is the experience gained with the study of DOM (introduced in the previous section) which is leveraged to modify the CPU to make it resistant against side-channel attacks. The authors split the processor in a protected and an unprotected part, and realise an ALU protected using the domain oriented approach to carry the needed basic operations. Experimental results show an increased resistance against side-channel attacks and a scale of the system almost linear with the order of protection.

Protection against power analysis attacks for the RISC-V processor have been also proposed by De Mulder et al. [MGH19]. The proposed solution aims at protecting against first-order power and electromagnetic attacks. The protection is achieved using a combination of known masking techniques and a masked access to memory. The second mask for accessing the memory is generated on the fly within the boundary of the CPU, and thus, at least in principle, robust. The leakage reduction is demonstrated by a number of practical experiments.

The use of instruction set extensions to increase the resistance of a processor against power analysis attacks has been explored also in the past. Tillich and Großschädl [TG07] evaluated the resistance against side-channel attacks of a processor extended with custom instructions for AES and proposed to implement the most security-critical operation of masking using a DPA-resistant logic style. A design flow for automatically implementing an instruction set extension using a protected logic style was presented by Regazzoni et al. [RCS<sup>+</sup>09] and evaluated on OpenRISC. The selection of the instructions was driven by a security metric and the protected logic style used was a MOS transistor-based current mode logic.

The most relevant work to our own is probably that of Kiaei and Schaumont [KS20]. They propose to extend the RISC-V processor with dedicated instructions to mitigate side-channel attacks, focusing in particular on DOM. Our paper shares the core idea of extending the instruction set of a processor to achieve side-channel resistance, but provides novel contributions. Firstly, our instructions are not limited to the case of DOM, but are suitable for implementing masking countermeasures in general and can protect a wide range of algorithms. Secondly, our instructions are integrated in the core allowing us to provide a quantitative analysis of the achieved robustness and of the performance overhead. Lastly, we show that it is possible to achieve security of masking using dedicated instructions without the need of duplicating the datapath to strongly separate the secure and insecure zone. To the best or our knowledge, previous works on instruction set extension for accelerating masking and for side-channel security in general, have always proposed to have such strong differentiation.

# **3** A design perspective

**Concept.** Focusing without loss of generality on use of Boolean masking, the ISE targets inclusion of instructions to support 1) binary masked operations, i.e.,  $\hat{r} = \hat{x} \ominus \hat{y}$  for some set of  $\ominus$ , 2) unary masked operations, i.e.,  $\hat{r} = \oslash \hat{x}$  for some set of  $\oslash$ , and 3) various auxiliary operations, such as conversion into, from, and between masked representations. The set of supported operations should be general-purpose in the sense they are useful for a range of cryptographic constructions and masking schemes; they often have an equivalent in, and so represent close to a "drop in" replacement for instructions in the base ISA by including, e.g.,  $\ominus \in \{\land, \lor, \oplus, +, -\}$  and  $\oslash \in \{\neg\}$  to mirror the unmasked Boolean operations already available. Doing so is complicated, however, by the fact that for n = 2 shares we have

$$\hat{r} = \hat{x} \ominus \hat{y} \implies (r_0, r_1) = (x_0, x_1) \ominus (y_0, y_1),$$

for example. That is, doing so increases the number of register indexes required, and, therefore, pressure on instruction encoding: an unmasked binary (resp. unary) operation requires 3 (resp. 2) register indexes, whereas a masked equivalent requires 6 (resp. 4). The same scenario is articulated by Lee et al. [LYS04], who describe and use the term Multi-word Operand, Multi-word Result (MOMR) to characterise and thereby distinguish cryptographic operations from the general case. There are various ways to satisfy this requirement: we use an implied approach, where two indexes are encoded as one, i.e.,  $(i, i + 1) \mapsto i$ . For example, the even-odd index pair (2, 3) is encoded as the first, even index 2; the second, odd index 3 is then implicit rather than explicit. This is a limited instance of the Register File Extension for Multi-word and Long-word Operation (RFEMLO) approach proposed by Lee and Choi [LC08].

The ISE itself constitutes 22 additional instructions, which can be divided into 4 feature classes. Table 1 offers a high-level summary of these instructions, with the underlying operations captured in an algorithmic format by Appendix B to avoid repetition inline; we discuss their design in detail below.

**Notation.** The RISC-V naming convention [RV:19, Section 27] for ISEs uses a string of single-character identifiers to specify features realised in an implementation. We adopt a variant of this approach, where, for example, ISE[CBA] denotes a concrete implementation of the ISE that supports the C, B, and A feature classes but not the F feature class.

We attempt to describe a given software implementation as precisely and clearly as possible, through consistent use of the following terminology. An *unmasked* implementation of some functionality represents an insecure (in the sense it includes no masking-based countermeasures) baseline, as realised using the base ISA only. In contrast, an *ISA-masked* or *ISE-masked* implementation will secure the associated unmasked baseline via masking, as realised using either the base ISA only or base ISA plus ISE respectively.

**Conversion (C-class).** The ISE includes a suite of instructions that support conversion of operands under Boolean masking to/from arithmetic masking. For example, the instruction

uses the input  $\hat{x} = (x_0, x_1) = (\mathsf{GPR}[\mathsf{rs1}], \mathsf{GPR}[\mathsf{rs2}])$  so  $x = x_0 \oplus x_1$ ; it computes the output  $\bar{r} = (r_0, r_1) = (\mathsf{GPR}[\mathsf{rd1}], \mathsf{GPR}[\mathsf{rd2}]) = \mathsf{BOOL2ARITH}((x_0, x_1))$  so  $r = r_0 + r_1 \pmod{2^w} = x$ .

**Operations under Boolean masking (B-class).** The ISE includes a suite of instructions that support Boolean masking. They allow masking, unmasking, remasking, and application

| 20<br>21<br>22                                                                                                                         | $15 \\ 16 \\ 17 \\ 18 \\ 19$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3<br>4<br>6<br>6<br>7<br>7<br>6<br>8<br>8<br>8<br>8<br>8<br>8<br>9<br>9<br>9<br>9<br>10<br>11<br>11<br>11<br>11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2 1                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Ţ                                                                                                                                      | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Class<br>C                                                                                                                          |

| <pre>mask.f.sqr (rd1,rd2), (rs1,rs2) → mask.f.mul (rd1,rd2), (rs1,rs2), (rs3,rs4) → mask.f.aff (rd1,rd2), (rs1,rs2), (rs3,rs4) →</pre> | <pre>mask.a.mask (rd1,rd2), rs1 mask.a.unmask rd1, (rs1,rs2) mask.a.remask (rd1,rd2), (rs1,rs2) mask.a.add (rd1,rd2), (rs1,rs2), (rs3,rs4) mask.a.sub (rd1,rd2), (rs1,rs2), (rs3,rs4)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <pre>mask.b.mask (rd1,rd2), rs1 mask.b.unmask rd1, (rs1,rs2) mask.b.remask (rd1,rd2), (rs1,rs2) mask.b.not (rd1,rd2), (rs1,rs2), (rs3,rs4) mask.b.ior (rd1,rd2), (rs1,rs2), (rs3,rs4) mask.b.sor (rd1,rd2), (rs1,rs2), (rs3,rs4) mask.b.s1li (rd1,rd2), (rs1,rs2), imm mask.b.sr1i (rd1,rd2), (rs1,rs2), imm mask.b.sori (rd1,rd2), (rs1,rs2), imm mask.b.sub (rd1,rd2), (rs1,rs2), imm mask.b.sub (rd1,rd2), (rs1,rs2), (rs3,rs4)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Syntax<br>mask.a2b (rd1,rd2), (rs1,rs2)<br>mask.b2a (rd1,rd2), (rs1,rs2)                                                            |

|                                                                                                                                        | $ \begin{array}{l} \mapsto \ ({\sf GPR[rd1]}, {\sf GPR[rd2]}) \leftarrow {\sf ArithMask}({\sf GPR[rs1]}) \\ \mapsto \ {\sf GPR[rd1]} \qquad \leftarrow {\sf ArithUnmask}(({\sf GPR[rs1]}, {\sf GPR[rs2]})) \\ \mapsto \ ({\sf GPR[rd1]}, {\sf GPR[rd2]}) \leftarrow {\sf ArithRemask}(({\sf GPR[rs1]}, {\sf GPR[rs2]}), ({\sf GPR[rs3]}, {\sf GPR[rs4]})) \\ \mapsto \ ({\sf GPR[rd1]}, {\sf GPR[rd2]}) \leftarrow {\sf ArithAdd}(({\sf GPR[rs1]}, {\sf GPR[rs2]}), ({\sf GPR[rs3]}, {\sf GPR[rs4]})) \\ \mapsto \ ({\sf GPR[rd1]}, {\sf GPR[rd2]}) \leftarrow {\sf ArithSub}(({\sf GPR[rs1]}, {\sf GPR[rs2]}), ({\sf GPR[rs3]}, {\sf GPR[rs4]})) \\ \end{array} $ | <pre> +→ (GPR[rd1], GPR[rd2]) ← BOOLMASK(GPR[rs1]) +→ GPR[rd1] ← BOOLUNMASK((GPR[rs1], GPR[rs2])) +→ (GPR[rd1], GPR[rd2]) ← BOOLREMASK((GPR[rs1], GPR[rs2])) +→ (GPR[rd1], GPR[rd2]) ← BOOLNOT((GPR[rs1], GPR[rs2]), (GPR[rs3], GPR[rs4])) +→ (GPR[rd1], GPR[rd2]) ← BOOLAND((GPR[rs1], GPR[rs2]), (GPR[rs3], GPR[rs4])) +→ (GPR[rd1], GPR[rd2]) ← BOOLSLL((GPR[rs1], GPR[rs2]), (GPR[rs3], GPR[rs4])) +→ (GPR[rd1], GPR[rd2]) ← BOOLSRL((GPR[rs1], GPR[rs2]), imm) +→ (GPR[rd1], GPR[rd2]) ← BOOLADD((GPR[rs1], GPR[rs2]), imm) +→ (GPR[rd1], GPR[rd2]) ← BOOLADD((GPR[rs1], GPR[rs2]), (GPR[rs3], GPR[rs4])) +→ (GPR[rd1], GPR[rd2]) ← BOOLADD((GPR[rs1], GPR[rs2]), GPR[rs3], GPR[rs4])) +→ (GPR[rd1], GPR[rd2]) ← BOOLADD((GPR[rs1],</pre> | Semantics<br>→ (GPR[rd1], GPR[rd2]) ← BOOL2ARITH((GPR[rs1], GPR[rs2]))<br>→ (GPR[rd1], GPR[rd2]) ← ARITH2BOOL((GPR[rs1], GPR[rs2])) |

Table 1: A summary of additional instructions that constitute the ISE, and their mapping onto underlying operations.

of operations to (masked) operands: these operations include NOT, AND, OR, XOR, leftand right-shift, right-rotate, addition, and subtraction. For example, the instruction

uses the inputs  $\hat{x} = (x_0, x_1) = (\mathsf{GPR}[\mathsf{rs1}], \mathsf{GPR}[\mathsf{rs2}])$  and  $\hat{y} = (y_0, y_1) = (\mathsf{GPR}[\mathsf{rs3}], \mathsf{GPR}[\mathsf{rs4}])$ so  $x = x_0 \oplus x_1$  and  $y = y_0 \oplus y_1$ ; it computes  $\hat{r} = (r_0, r_1) = (\mathsf{GPR}[\mathsf{rd1}], \mathsf{GPR}[\mathsf{rd2}]) = \mathsf{BOOLADD}((x_0, x_1), (y_0, y_1))$  so  $r = r_0 \oplus r_1 = x + y$ .

**Operations under arithmetic masking (A-class).** The ISE includes a suite of instructions that support arithmetic masking. They allow masking, unmasking, remasking, and application of operations to (masked) operands: these operations include addition and subtraction. For example, the instruction

mask.a.sub (rd1,rd2), (rs1,rs2), (rs3,rs4)

uses the inputs  $\bar{x} = (x_0, x_1) = (\text{GPR}[rs1], \text{GPR}[rs2])$  and  $\bar{y} = (y_0, y_1) = (\text{GPR}[rs3], \text{GPR}[rs4])$ so  $x = x_0 + x_1 \pmod{2^w}$  and  $y = y_0 + y_1 \pmod{2^w}$ ; it computes  $\bar{r} = (r_0, r_1) = (\text{GPR}[rd1], \text{GPR}[rd2]) = \text{ARITHSUB}((x_0, x_1), (y_0, y_1))$  so  $r = r_0 + r_1 \pmod{2^w} = x - y$ .

**Operations for field arithmetic (F-class).** Arithmetic operations in the finite field  $\mathbb{F}_{2^8}$  play an essential role in many symmetric cryptosystems, most notable the AES [DR02]. For example, the SubBytes transformation of the AES performs an inversion of an element of  $\mathbb{F}_{2^8}$ , followed by an affine transformation. The MixColumns transformation can be interpreted as multiplications of polynomials whose coefficients are elements of  $\mathbb{F}_{2^8}$ . Besides the AES, many other symmetric cryptosystems involve arithmetic operations in  $\mathbb{F}_{2^8}$ ; these include the block ciphers SM4 and Camellia, the hash function Grøstl, the authenticated encryption algorithms COMET and Saturnin (which made it into the second round of the current NIST lightweight cryptography standardisation project), and many more.

When it comes to masking of the AES (and AES-like or AES-inspired designs), two basic approaches received particular attention in the recent literature. The first approach uses a bit-sliced implementation as starting point and applies masking to the underlying logical operations [SS16]. Such masked bit-sliced implementations are attractive because they can reach relatively high throughput; for example, Schwabe and Stoffelen [SS16] report an encryption time of 7422.6 cycles per block for first-order masked AES on a Cortex-M4 micro-controller when encrypting 256 consecutive blocks. However, the main disadvantage of bit-slicing is that it can only be applied to non-feedback modes of operation like counter mode. In addition, bit-slicing introduces a disproportionately high overhead when the amount of data to be encrypted is small, as is often the case for applications that run on constrained devices. An alternative approach is the well-known masking technique of Rivain and Prouff [RP10], which is provably secure in the probing model and can be straightforwardly extended to higher orders. The Rivain-Prouff masking technique requires performing the inversion in  $\mathbb{F}_{2^8}$  through a sequence of multiplication and squarings along with mask refreshings to inject independent randomness. When properly implemented, the Rivain-Prouff masking can meet the strong theoretical security promises in practice, but introduces a massive penalty in execution time. For example, a first-order masked implementation of AES-128 on an ARM Cortex-M3 micro-controller is between 40 and 60 times slower than unprotected reference implementation [GR17].

The B-class instructions described above, most notably mask.b.xor and mask.b.and, can be applied for Boolean masking of bit-sliced implementations of any symmetric cryptosystem, including the AES. However, given the mentioned limitations of bit-slicing (most notably the restriction to non-feedback modes of operation), which carry over to masked bit-slicing, it makes sense to define an ISE to support the masking of nonbitsliced implementations of the AES. The SubBytes transformation deserves particular attention since it includes inversion in  $\mathbb{F}_{2^8}$ , which is non-linear and, therefore, extremely costly to mask. Rivain and Prouff [RP10] proposed to mask **SubBytes** by performing a sequence of masked multiplications and squarings in  $\mathbb{F}_{2^8}$ , followed by a masked affine transformation. The masked multiplication and squaring are, in turn, composed of "ordinary" multiplications and squarings in  $\mathbb{F}_{2^8}$ , which are usually implemented using lookup tables (cf. [GR17, Section 3]). However, look-up tables add to the memory footprint and may enable cache attacks when executed on devices with a data cache. Said problems can be easily overcome by defining instructions for multiplication, squaring, and affine transformation in  $\mathbb{F}_{2^8}$ . These operations are ubiquitous in symmetric cryptography (cf. SM4, Camellia, Grøstl, etc.), which means ISEs for masked multiplication, masked squaring, and masked affine transformation are in line with the general design concept described at the beginning of this section, namely to support operations that are general-purpose and useful for a wide range of cryptographic constructions. For example, the instruction

```

mask.f.mul (rd1,rd2), (rs1,rs2), (rs3,rs4)

```

executes a masked 4-way SIMD Within a Register (SWAR) multiplication in  $\mathbb{F}_{2^8}$ , interpreting the operand in each source register as four elements of  $\mathbb{F}_{2^8}$ . This instruction is basically a "packed" version of the masked  $\mathbb{F}_{2^8}$  multiplication described by Rivain and Prouff [RP10]; a more formal specification of mask.f.mul can be found in Appendix B. Also the mask.f.sqr and mask.f.aff instruction execute a masked squaring and masked affine transformation in a 4-way SWAR-parallel fashion, which means they operate on four bytes in parallel, whereby each byte is interpreted as an element of  $\mathbb{F}_{2^8}$ . In essence, mask.f.mul and mask.f.aff can be seen as 32-bit versions of the x86 instructions GF2P8MULB [X8618, Pages 3-447–3-448] and GF2P8AFFINEQB [X8618, Pages 3-445–3-446]. Both mask.f.mul and mask.f.sqr use the irreducible polynomial of the AES, namely  $p(x) = x^8 + x^4 + x^3 + x + 1$ . Nonetheless, these instructions can still be used for e.g., SM4 and other cryptosystems that use a different irreducible polynomial, since the corresponding field-representations are isomorphic.

## 4 A hardware perspective: ISE realisation

In this section we consider the ISE from a hardware perspective, i.e., how the ISE is realised. Section 4.1 outlines the implementation of a masked ALU module, and integration of said module into an existing RISC-V compliant micro-architecture. Section 4.2 then presents synthesis results, including area, plus analysis of per-instruction (versus whole kernel) execution properties including execution latency, memory footprint, and leakage.

In common with the ISA, our ISE defines an interface; this implies a degree of flexibility with respect to any implementation of it. As a result, we stress that ours is *an* implementation rather than *the* (only possible) implementation: alternative approaches that yield incremental improvements may be viable, and in fact may be necessary to support integration with different micro-architectures.

#### 4.1 Implementation

#### 4.1.1 Implementation of a masking-specific ALU

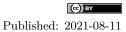

Each operation underlying an ISE instruction is evaluated using a masked ALU module, an illustrative block diagram of which is shown in Figure 1: it accepts two 2-share inputs (s2\_opr\_a,s2\_opr\_b) and (s2\_opr\_c,s2\_opr\_d) and produces one 2-share output (s3\_opr\_a,s3\_opr\_b), where, for both input and output, only 1 share may be used in specific cases such as masking and unmasking. Internally, the ALU can be viewed as a collection of submodules which cater for four cases, namely 1) support for random bit

**Figure 1:** A block diagram illustrating submodules of the masked ALU module, and their internal organisation. Note that, for clarity, we use 2-share connections (i.e., each connection communicates two, 32-bit shares) throughout and omit all connections stemming from the two RBG instances: these are used by almost all other components.

generation, 2) support for B-class instructions, 3) support for A-class instructions, and 4) support for F-class instructions, which we expand upon below.

**High-level implementation strategy.** The masked ALU supports a variety of operations, each of which could be classified as either linear or non-linear. Whereas linear operations (e.g., masked XOR) can operate independently on the shares involved, the same is not true of non-linear operations (e.g., masked AND): because they involve operations which allow interaction between shares, their leakage-free implementation demands care with respect to glitches, i.e., transient changes to the state of a signal before it finally becomes stable. Per Section 2.2, various implementation strategies, such as TI [NRR06] and DOM [GMK16], can be used to address this challenge. We opt for a DOM-based strategy, which, at a high level, requires the application of two principles: 1) separation of a given module into domains, each of which operates on associated shares and is therefore inherently robust against glitches, and 2) insertion of latching and remasking steps, which cater for cross-domain operations by preventing glitches and therefore associated leakage. Based on these principles, we apply several general strategies throughout the implementation of given operation:

1. By default, insertion of an additional latching step within a given module would imply an additional clock cycle of latency; this would then be reflected in the latency of instruction execution, and thus instruction throughput overall. To avoid this overhead, we use double-pumped clocking. As a result of the short critical paths involved, we can make use of both positive (for input and output registers) and

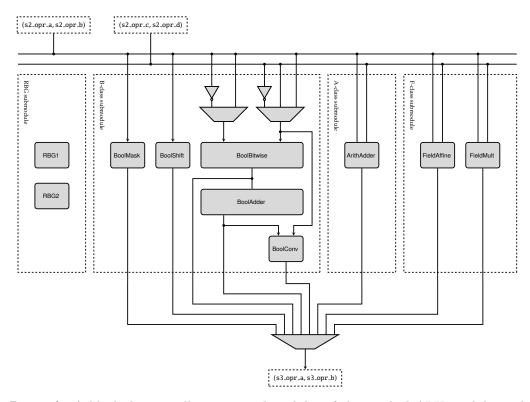

(b) Boolean masked (packed) field multiplication module.

**Figure 2:** Two circuit diagrams which capture the DOM-based implementation of selected operations: note 1) the inclusion of remasking steps, and 2) double-pumped approach to clocking, whereby the input and output (resp. latching step) registers are enabled by positive (resp. negative) clock edges.

negative (for registers associated with the additional latching step) clock edges and thus avoid additional latency.

- 2. Although remasking steps are only *required* if/where cross-domain operations exist, the relative abundance of randomness (versus in software) means we are able to insert additional remasking steps elsewhere: this is a conservative decision with respect to leakage, and allows the ALU to be more modular by removing various assumptions about use of and interaction between modules.

- 3. The general DOM-based strategy includes more specific variants termed DOM-indep and DOM-dep, which cater for cases where the inputs are known to be independent or dependent respectively. We carefully select between these variants depending on the context, and so avoid leakage but *also* optimise the implementation where possible.

Although it is possible to apply tools such REBECCA [BGI<sup>+</sup>18], maskVerif [BBC<sup>+</sup>19], and SILVER [KSM20] to formally verify properties of some smaller, isolated modules within the masked ALU, we faced various challenges when doing so in general: these included 1) the general complexity, e.g., total number of gates, and 2) the use of an iterative rather than combinatorial architecture for the Kogge-Stone [KS73] adder supporting Boolean masked addition and subtraction. Our strategy is therefore most fairly described as "glitch free by construction then empirical validation", rather than as "glitch free by formal verification" for example.

**RBG submodule.** The RBG submodule generates random masks for (re)masking operations: at most two such masks are required by the ALU for any given operation, so it includes two instances. Each instance uses a hybrid design, motivated by the trade-off between area, throughput, and randomness quality, which includes both pseudo- and true-random components.

The basis for this design is a 32-bit Linear Feedback Shift Register (LFSR), which uses a feedback function selected [GA] to generate a maximal length pseudo-random sequence of  $2^{32} - 1$  outputs. The LFSR is free-running in the sense it is updated every clock cycle, rather, for example, than per use of the masked ALU. The LFSR state in some *i*-th clock cycle is used as is to form the output and hence a 32-bit mask; the state is not architecturally visible, and therefore cannot be read from or written to by software.

In principle at least, the inherently deterministic behaviour of such an LFSR could be exploited in an attack. To address this fact we add selected non-determinism by injecting a single true-random bit into the feedback function. This bit is generated by an implementation of the ES-TRNG design due to Yang et al. [YRG<sup>+</sup>18], which relies on the timing jitter of a ring oscillator; we employ a third-order parity filter to post-process the raw output. As well as enhancing the security characteristics of the LFSR, doing so also acts as a way to seed it: one simply stalls for some n clock cycles, after which ntrue-random bits have been injected into and so act to seed the LFSR state.

**B-class submodule.** The B-class submodule is realised by a set of fairly independent modules which collectively provide functionality in support of the B-class instructions. The internal organisation of said modules is area-optimised, in the sense that, if and where appropriate, 1) common functionality is reused between operations, and 2) functionality supporting a given operation can be iterative (or multi-cycle) versus combinatorial (or single-cycle). The BoolMask module computes Boolean masking and remasking. The BoolShift module computes Boolean masked left-shift, right-shift, and right-rotate. The BoolBitwise module computes bitwise operations, including Boolean masked NOT, XOR, and AND; Boolean masked OR is computed using the Boolean masked AND module by

applying De Morgan's law. Boolean masked addition and subtraction are computed by the BoolBitwise and BoolAdder modules, which are combined to form an iterative Kogge-Stone [KS73] adder. The former realises the pre-processing step, while the latter realises the iteration, and post-processing steps. A set of registers is used to latch the output of each *i*-th step of iteration ready for use in the subsequent, (i + 1)-th step. Finally, the BoolConv module reuses Boolean masked addition and subtraction to allow conversion between Boolean and arithmetic masking.

The Boolean masked AND operations in the BoolBitwise and BoolAdder modules are supported by DOM-dep and DOM-indep implementations respectively. The former case must be pessimistic because the inputs are externally generated (so may be dependent); the latter case can be optimistic because the inputs are internally generated (so can be guaranteed independent), and, as a result, is more efficient. Figure 2a describes the former, i.e., a DOM-dep, Boolean masked AND module: this clearly demonstrates points in our high-level implementation strategy, namely the use of 1) two domains (essentially the left-and right-hand side of the circuit), 2) one latching step (driven by the negative edge of clk, 3) two remasking steps (one at the input to the latching step using RBG1, one at the module output using RBG2).

**A-class submodule.** The A-class submodule is realised by a set of fairly independent modules which collectively provide functionality in support of the A-class instructions. The ArithAdder module computes arithmetic masked addition and subtraction.

**F-class submodule.** The F-class submodule is realised by a set of fairly independent modules which collectively provide functionality in support of the F-class instructions. The FieldAffine module computes a (packed) masked field transform (or matrix-vector product). The FieldMult module computes a (packed) masked field multiplication.

Both Boolean masked (packed) masked field multiplication and squaring operations in the FieldMult module are supported by a DOM-indep implementation. Figure 2b describes the implementation, which follows that described by Rivain and Prouff [RP10, Section 3.1], using instances an optimised design [fSN] for the constituent (unmasked) multiplications in  $\mathbb{F}_{2^8}$ ; the multiplexers before the  $\mathbb{F}_{2^8}$  multipliers are controlled to allow either multiplication or squaring.

Although DOM-indep assumes the inputs are independent, the major reason for dependency would be where the inputs are equal: this is allowed via a separate controlpath, i.e., a Boolean masked (packed) masked field squaring operation. Table 4 captures this assumption, which then forms part of the hardware/software interface: responsibility for 1) correct selection between multiplication and squaring, and 2) satisfaction of the independence assumption for multiplication lies with software. We stress that it is possible to opt for a DOM-dep implementation instead, which then shifts the trade-off toward usability (by removing said assumption) at the cost of efficiency.

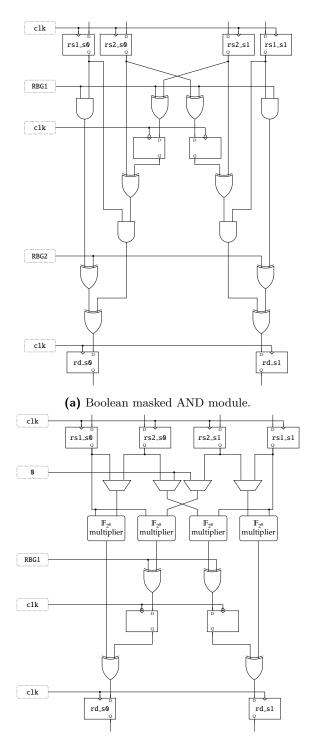

### 4.1.2 Integration of the masked ALU into a RISC-V compliant micro-architecture

The masked ALU described in Section 4.1.1 was integrated into the SCARV<sup>2</sup> core, a micro-controller class 5-stage pipelined micro-architecture that implements RV32IMCB, i.e., the RV32I base ISA plus the M(ultiply) [RV:19, Chapter 7], C(ompressed) [RV:19, Chapter 16] and (draft) B(it manipulation) [RV:19, Chapter 17]<sup>3</sup> standard extensions. We supplement this baseline core with an instruction

$\texttt{rbgsamp rd} \quad \mapsto \quad \mathsf{GPR}[\texttt{rd}] \xleftarrow{\$} \{0,1\}^{\text{XLEN}},$

<sup>&</sup>lt;sup>2</sup>https://github.com/scarv/scarv-cpu

<sup>&</sup>lt;sup>3</sup> See also https://github.com/riscv/riscv-bitmanip

**Figure 3:** A block diagram illustrating integration of the masked ALU into the SCARV core. Note that registers and wires are coloured blue (resp. red) to reflect their relationship with the 0-th (resp. 1-st) share of intermediate, in-flight values; green modules represent the memory interface, careful use of which is important to ensure leakage-free transfer of shares between general-purpose registers and memory.

which samples XLEN bits from an underlying Random Bit Generator (RBG)<sup>4</sup> and stores the result into a general-purpose register. This is important, because it allows efficient generation of masks in software which uses the base ISA, i.e., it does not artificially penalise the base ISA versus the ISE with respect to generation of randomness.

A block diagram of the core is show in Figure 3. Note that the core is interfaced with a 64 kB RAM (left) and a 1 kB ROM (top); both have single-cycle access latencies.

**Support for paired register file access.** Per Section 3, the masked ISE design demands a general-purpose register file which can support paired read (resp. write) access: for masked operands, an index i implies a need to read from (resp. write to) both  $\mathsf{GPR}[i]$  (i.e., the 0-th share) and  $\mathsf{GPR}[i+1]$  (i.e., the 1-st share).

Due to the indexing scheme, restructuring the register file to support such access was fairly straightforward. Specifically, the odd and even registers were split into two groups (or sub-files), each one using a dedicated 16-to-1 multiplexer tree to support read access. This approach means a) both elements of a pair can be accessed in parallel, b) there is no interaction between elements within the multiplexer tree, and c) an underlying implementation based on either flip-flops or latches *or* SRAM is feasible. For single-register reads, an additional 2-to-1 multiplexer in the decode stage selects between either the odd or even group based on the least-significant bit of the index. For base ISA instructions rs1 is stored in s2\_opr\_a and rs2 is stored in s2\_opr\_b. For ISE instructions the 0-th (resp. 1-st) share of rs1 is stored in s2\_opr\_a (resp. s2\_opr\_c), whereas the 0-th (resp. 1-st) share of rs2 is stored in s2\_opr\_b (resp. s2\_opr\_d); for the SCARV core at least, this meant adding an additional pipeline register, i.e., s2\_opr\_d.

**Mitigating the impact of accidental share combination.** We found that although implementation of a leakage-free masked ALU was straightforward in isolation, integration with the core presented some more subtle challenges from a leakage perspective. In particular, given the masked representation of some x, i.e.,  $\tilde{x} = (x_0, x_1)$ , potential sources for accidentally share combination, i.e., interaction between  $x_0$  and  $x_1$ , occur throughout the execution pipeline. One way to address this challenge (see, e.g., [KS20, Figure 1]), is by executing base ISA and ISE instructions using separate insecure and secure datapaths. We instead opted to address it in an integrated datapath, employing two mechanisms.

At an intra-component level, note that the interleaved mapping of shares to pipeline registers is an intentional design decision: the mapping acts to prevent both shares of either rs1 or rs2 entering a functional unit other than the masked ALU, and so eliminates the potential for accidental share combination within such components. At an inter-component level, we adopt a representation where the 1-st share is bit-reversed; this is applied to both the register file and pipeline registers. As a result, any accidental share combination, e.g., switching between shares in the forwarding network, will cause non-corresponding bits of those shares to interact: the 0-th bit of the 0-th share will interact with the (XLEN - 1)th bit of the 1-st share rather than the 0-th bit of the 1-st share, for example. The representation is managed dynamically and automatically in hardware, so is transparent to software. Instructions from the base ISA unreverse their operands before being stored in the s2\_opr\_a and s2\_opr\_b pipeline registers. Instructions from the ISE unreverse their operands before entering the execute stage, immediately before the masked ALU; the 1-st share is rereversed immediately after the masked ALU, before entering the multiplexer tree that selects the next value stored in the s3\_opr\_b pipeline register. This mechanism is inexpensive to realise in hardware: it requires 1) a 1-bit flag per general-purpose and pipeline register to track reversed'ness, and 2) a 2-to-1 multiplexer per pipeline register to realise (un)reversal where required.

$<sup>^{4}</sup>$ Note that this mechanism is distinct from the random bit generator(s) used by the masked ALU, although uses the same design.

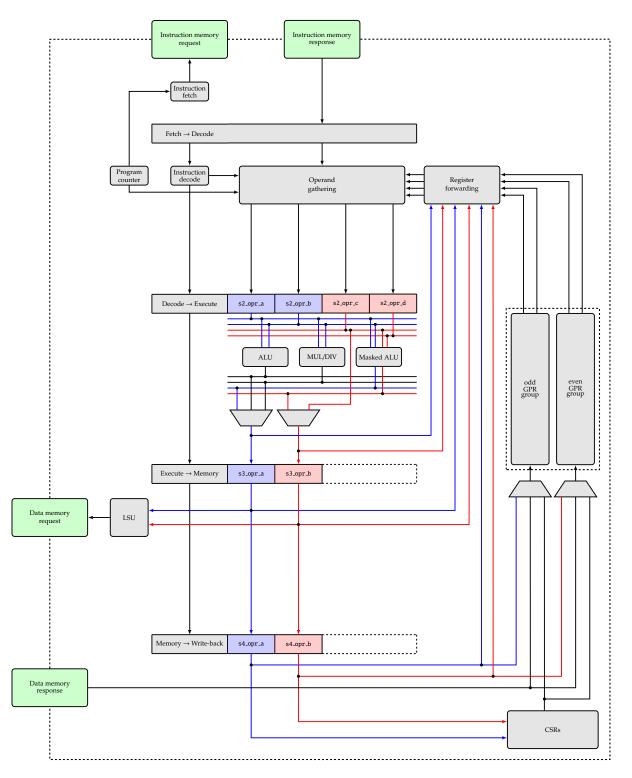

**Table 2:** Synthesis results for the ISE, as integrated into the SCARV core: the rows capture 1) the baseline core with no ISE, 2) the baseline core plus ISE with C, B, and A classes, and 3) the baseline core plus ISE with C, B, A, and F classes. Note that timing slack is quoted for a frequency of f = 50 MHz. for FPGA, while the ASIC designs have been all synthesized imposing a clock of 4ns.

| Implementation                                                | LUTs                                                                                            | FPGA<br>FFs                                                                                     | Timing slack                     | ASIC<br>GE                                                                                         |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------|

| SCARV core<br>SCARV core + ISE[CBA]<br>SCARV core + ISE[CBAF] | $\begin{array}{c} 4229 \ (1.0\times) \\ 6602 \ (1.56\times) \\ 7676 \ (1.82\times) \end{array}$ | $\begin{array}{c} 2141 \ (1.0\times) \\ 2606 \ (1.24\times) \\ 2670 \ (1.25\times) \end{array}$ | 3.417 ns<br>1.012 ns<br>1.833 ns | $\begin{array}{c} 35887 \ (1.0\times) \\ 46152 \ (1.29\times) \\ 52016 \ (1.45\times) \end{array}$ |

We prevent the accidental unreversing of shares in the decode stage by gating the unreverse enable control signal with a negative edge triggered flip-flop. The flip-flop prevents glitches in the control signal, and is updated if and only if an unreversed representation is required.

Overall, these mechanisms allow selective sharing of datapath components in a leakageconsiderate manner: they reduce area versus the alternative, while also avoiding leakage *plus* added latency that may stem from forwarding between base ISA and ISE instructions.

**Verifying functional correctness.** Functional correctness of some Design Under Test (DUT), in our case the baseline core plus ISE, is a property which captures whether execution of instructions complies with their specification. There are essentially two options for checking this property: 1) given known input, check whether a specific output is produced, and 2) given known input, check whether a relationship holds between said input and the output produced.

The first option offers the strongest assurance that instruction execution matches the associated specification, and enables co-simulation of the DUT with a golden reference model (e.g., QEMU or OVPSim) or formal specification. However, the nature of masking and thus ISE support for it *demands* that input and output shares are randomised: a relationship between the input and output shares is specified, but their concrete values are not. As a result, use of co-simulation based verification requires auxiliary input (or "hints") to ensure the model and DUT are synchronised: this becomes complex to maintain, even for simple DUTs. We therefore employed the second option, specifically Bounded Model Checking (BMC), to *prove* relationships between input and output shares are *always* correct without a need to know their value. For example, for the instruction

mask.b.xor (rd1,rd2), (rs1,rs2), (rs3,rs4)

we prove the relationship  $r = x \oplus y$  holds for x = BOOLUNMASK((GPR[rs1], GPR[rs2])), y = BOOLUNMASK((GPR[rs3], GPR[rs4])), and r = BOOLUNMASK((GPR[rd1], GPR[rd2])). The baseline core was already formally verified using the riscv-formal<sup>5</sup> framework, which we extended to support paired register file access. This enabled verification of the base ISA instructions, ISE instructions, and interaction between them (having included checks for access consistency).

### 4.2 Evaluation

**Experimental platform.** The augmented SCARV core was implemented on a SASEBO-GIII [HKSS12] side-channel analysis platform, which houses two FPGAs: a Xilinx Kintex-7 (model xc7k160tfbg676) target FPGA, and a Xilinx Spartan-6 (model xc6s1x45) support FPGA. We use the former exclusively, synthesising stand-alone designs for it using Xilinx Vivado 2019.2; default synthesis settings are used, with no effort invested in synthesis or

<sup>&</sup>lt;sup>5</sup>https://github.com/SymbioticEDA/riscv-formal

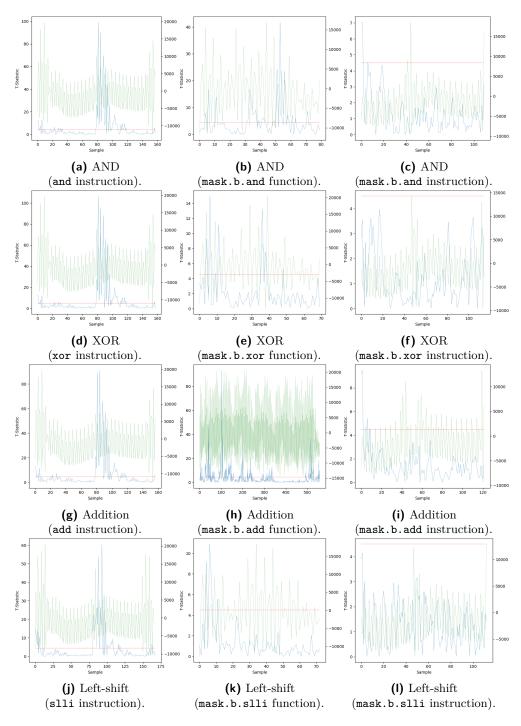

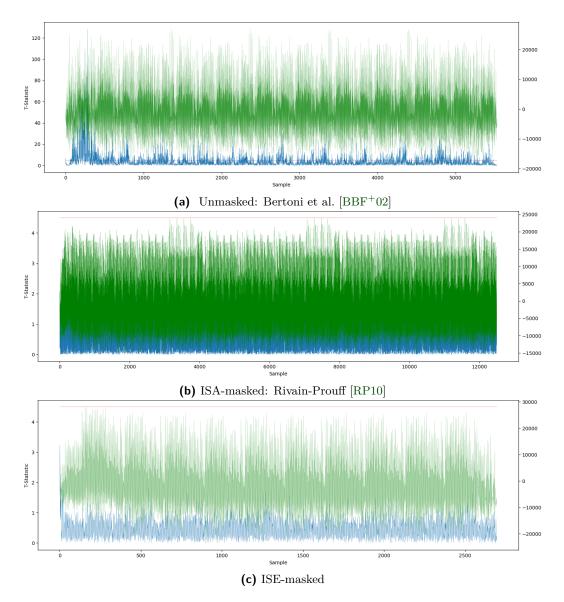

**Figure 4:** Comparison of leakage for selected instructions as executed on the SCARV core, for unmasked (left), ISA-masked (middle), and ISE-masked (right) cases. Each case relates to a set of 100,000 power consumption traces: the green plot shows the average of said traces, whereas the blue plot shows the (absolute) t-statistic stemming application of TVLA-based leakage detection to them.

**Table 3:** Comparison of a) cycle count (i.e., execution latency), b) instruction count (i.e., number of instructions executed), and c) instruction footprint (measured in bytes), for both unmasked (using the base ISA) and masked (using the base ISA and ISE) variants of individual, underlying operations. Entries marked – are not applicable, e.g., because there is no need for mask or unmask operations in the unmasked variant. Note for cycle counts, we count entire rising-edge to rising-edge clock cycles: this means operations such as BOOLAND which use double-pumped clocking take one cycle, despite a need for additional latching steps.

| Cycle Instruction Instruction |          |                           |              |          |                           |              |           |              |               |  |  |  |

|-------------------------------|----------|---------------------------|--------------|----------|---------------------------|--------------|-----------|--------------|---------------|--|--|--|

|                               |          | ount                      |              |          | ount                      | on           | footprint |              |               |  |  |  |

| Operation                     |          |                           | -            |          |                           |              |           |              |               |  |  |  |

|                               | Unmasked | ISA-masked                | ISE-masked   | Unmasked | ISA-masked                | ISE-masked   | Unmasked  | ISA-masked   | ISE-masked    |  |  |  |

|                               | sk       | as                        | as           | sk       | as                        | as           | l sk      | as           | as            |  |  |  |

|                               | ma       | Ë                         | Ë            | ma       | Ë                         | Ë            | L Ba      | Ë            | Ë             |  |  |  |

|                               | Ini      | Ā                         | Ц            | In       | Ā                         | Ц            | l i l     | Ā            | ц             |  |  |  |

|                               | ſ        | $\mathbf{I}_{\mathbf{S}}$ | $\mathbf{S}$ | 2        | $\mathbf{I}_{\mathbf{S}}$ | $\mathbf{S}$ | L<br>L    | $\mathbf{S}$ | $\mathbf{IS}$ |  |  |  |

| BOOL2ARITH                    | -        | 249                       | 6            | -        | 205                       | 1            | -         | 380          | 4             |  |  |  |

| Arith2Bool                    | —        | 268                       | 6            | -        | 220                       | 1            | -         | 440          | 4             |  |  |  |

| BoolMask                      | -        | 3                         | 1            | -        | 3                         | 1            | -         | 12           | 4             |  |  |  |

| BoolUnmask                    | -        | 1                         | 1            | -        | 1                         | 1            | -         | 4            | 4             |  |  |  |

| BoolRemask                    | —        | 3                         | 1            | -        | 3                         | 1            | -         | 12           | 4             |  |  |  |

| BOOLNOT                       | 1        | 1                         | 1            | 1        | 1                         | 1            | 4         | 4            | 4             |  |  |  |

| Booland                       | 1        | 7                         | 1            | 1        | 7                         | 1            | 4         | 28           | 4             |  |  |  |

| BOOLIOR                       | 1        | 6                         | 1            | 1        | 6                         | 1            | 4         | 24           | 4             |  |  |  |

| BOOLXOR                       | 1        | 3                         | 1            | 1        | 3                         | 1            | 4         | 12           | 4             |  |  |  |

| BoolSLL                       | 1        | 5                         | 1            | 1        | 5                         | 1            | 4         | 20           | 4             |  |  |  |

| BOOLSRL                       | 1        | 5                         | 1            | 1        | 5                         | 1            | 4         | 20           | 4             |  |  |  |

| BOOLROR                       | 1        | 8                         | 1            | 1        | 8                         | 1            | 4         | 32           | 4             |  |  |  |

| BoolAdd                       | 1        | 225                       | 6            | 1        | 193                       | 1            | 4         | 336          | 4             |  |  |  |

| BoolSub                       | 1        | 244                       | 6            | 1        | 211                       | 1            | 4         | 408          | 4             |  |  |  |

| ArithMask                     | -        | 3                         | 1            | -        | 3                         | 1            | -         | 12           | 4             |  |  |  |

| ArithUnmask                   | _        | 1                         | 1            | -        | 1                         | 1            | -         | 4            | 4             |  |  |  |

| ArithRemask                   | -        | 3                         | 1            | _        | 3                         | 1            | -         | 12           | 4             |  |  |  |

| ArithAdd                      | 1        | 2                         | 1            | 1        | 2                         | 1            | 4         | 8            | 4             |  |  |  |

| ArithSub                      | 1        | 2                         | 1            | 1        | $^{2}$                    | 1            | 4         | 8            | 4             |  |  |  |

| FieldSqr                      | 284      | 229                       | 1            | 115      | 185                       | 1            | 52        | 604          | 4             |  |  |  |

| FieldMul                      | 261      | 393                       | 1            | 121      | 339                       | 1            | 54        | 1180         | 4             |  |  |  |

| FieldAff                      | 28       | 704                       | 1            | 21       | 144                       | 1            | 50        | 400          | 4             |  |  |  |

**Table 4:** For each masked underlying operation as implemented using the ISE, a description of a) the number of fresh masks used, and b) whether dependent inputs are allowed ( $\checkmark$ ), i.e., the ALU will apply any remasking required, disallowed ( $\varkappa$ ), i.e., the user must apply any remasking required, or not applicable (-), i.e., either 0 or 1 masked input(s) is used.

| 11          |            |             |  |  |  |  |  |

|-------------|------------|-------------|--|--|--|--|--|

| Operation   | Randomness | Constraints |  |  |  |  |  |

| BOOL2ARITH  | 13         | -           |  |  |  |  |  |

| Arith2Bool  | 13         | _           |  |  |  |  |  |

| BoolMask    | 1          | -           |  |  |  |  |  |

| BoolUnmask  | 0          | -           |  |  |  |  |  |

| BoolRemask  | 1          | -           |  |  |  |  |  |

| BOOLNOT     | 1          | -           |  |  |  |  |  |

| BOOLAND     | 2          | 1           |  |  |  |  |  |

| BOOLIOR     | 2          | ✓           |  |  |  |  |  |

| BOOLXOR     | 1          | ✓           |  |  |  |  |  |

| BOOLSLL     | 1          | -           |  |  |  |  |  |

| BOOLSRL     | 1          | -           |  |  |  |  |  |

| BOOLROR     | 1          | -           |  |  |  |  |  |

| BoolAdd     | 12         | ✓           |  |  |  |  |  |

| BOOLSUB     | 12         | 1           |  |  |  |  |  |

| ArithMask   | 1          | -           |  |  |  |  |  |

| ArithUnmask | 0          | -           |  |  |  |  |  |

| ArithRemask | 1          | -           |  |  |  |  |  |

| ArithAdd    | 0          | 1           |  |  |  |  |  |

| ArithSub    | 0          | 1           |  |  |  |  |  |

| FieldSqr    | 1          | _           |  |  |  |  |  |

| FieldMul    | 1          | ×           |  |  |  |  |  |

| FieldAff    | 1          | -           |  |  |  |  |  |

post-implementation optimisation. The FPGA uses a 200 MHz differential external clock source, which is transformed into a 25 MHz internal clock signal for use by the core itself.

A standard pipeline of components is attached to the SASEBO-GIII, allowing acquisition of power consumption traces. These components include a MiniCircuits BLK+89 D/C blocker, a MiniCircuits SLP-30+ 32 MHz low-pass filter, an Agilent 8447D amplifier (with a 100 kHz to 1.3 GHz range, and 25 dB gain), and a PicoScope 5000 series oscilloscope; the latter is configured to use a 250 MHz sample frequency, and 12-bit sampling resolution. Coordination of the acquisition process is managed by a workstation connected to each component: it is tasked with 1) configuration of the FPGA with a synthesised bit-stream, 2) upload of software, as generated by a RISC-V capable instance of the GNU tool-chain<sup>6</sup> including GCC 8.2.0, to the core via a simple boot-loader, 3) communication of input and output to and from the core via a UART-based connection, and 4) configuration and download of traces from the oscilloscope.

Initial experiments with the baseline core highlighted some noise inherent in the acquisition pipeline. This noise was removed post-acquisition using a software-based filter. Specifically, a Butterworth [But30] low-pass filter with 5 taps and a 8 MHz cut-off frequency was used; the 8 MHz cut-off was selected so as to maximise detectable leakage during execution of base ISA instructions.