# Probing Security through Input-Output Separation and Revisited Quasilinear Masking

Dahmun Goudarzi<sup>1</sup>, Thomas Prest<sup>2</sup>, Matthieu Rivain<sup>3</sup> and Damien Vergnaud<sup>4,5</sup>

Independent researcher

dahmun.goudarzi@gmail.com

2 PQShield, Oxford, United Kingdom

thomas.prest@pqshield.com

CryptoExperts, Paris, France

matthieu.rivain@cryptoexperts.com

**Abstract.** The probing security model is widely used to formally prove the security of masking schemes. Whenever a masked implementation can be proven secure in this model with a reasonable leakage rate, it is also provably secure in a realistic leakage model known as the noisy leakage model. This paper introduces a new framework for the composition of probing-secure circuits. We introduce the security notion of input-output separation (IOS) for a refresh gadget. From this notion, one can easily compose gadgets satisfying the classical probing security notion -which does not ensure composability on its own- to obtain a region probing secure circuit. Such a circuit is secure against an adversary placing up to t probes in each gadget composing the circuit, which ensures a tight reduction to the more realistic noisy leakage model. After introducing the notion and proving our composition theorem, we compare our approach to the composition approaches obtained with the (Strong) Non-Interference (S/NI) notions as well as the Probe-Isolating Non-Interference (PINI) notion. We further show that any uniform SNI gadget achieves the IOS security notion, while the converse is not true. We further describe a refresh gadget achieving the IOS property for any linear sharing with a quasilinear complexity  $\Theta(n \log n)$  and a  $O(1/\log n)$  leakage rate (for an *n*-size sharing). This refresh gadget is a simplified version of the quasilinear SNI refresh gadget proposed by Battistello, Coron, Prouff, and Zeitoun (ePrint 2016). As an application of our composition framework, we revisit the quasilinear-complexity masking scheme of Goudarzi, Joux and Rivain (Asiacrypt 2018). We improve this scheme by generalizing it to any base field (whereas the original proposal only applies to field with nth powers of unity) and by taking advantage of our composition approach. We further patch a flaw in the original security proof and extend it from the random probing model to the stronger region probing model. Finally, we present some application of this extended quasilinear masking scheme to AES and MiMC and compare the obtained performances.

Keywords: Probing Security · Composition · Quasilinear Masking · IOS Notion

#### 1 Introduction

In cryptography, side-channel attacks are all attacks based on extracting information from a physical implementation of a cryptosystem. Rather than exploiting some weakness in

Licensed under Creative Commons License CC-BY 4.0.

Received: 2020-10-15 Accepted: 2020-12-15 Published: 2021-07-09

<sup>&</sup>lt;sup>4</sup> Sorbonne Université, CNRS, LIP6, Paris, France

<sup>&</sup>lt;sup>5</sup> Institut Universitaire de France, Paris, France

the underlying cryptographic algorithm, the leakage information is exploited by attackers to extract the secret key from a specific implementation.

Probing security is a notion put forward by Ishai, Sahai and Wagner in [ISW03] to evaluate the security of a circuit against a class of physical attacks. Specifically, they consider t-probing attacks in which the adversary has the ability to place some probes on t wires of a circuit processing some secrets. The circuit is said to be t-probing secure if no information leaks from the values of the t probed wires. More formally, one should be able to perfectly simulate the distribution of the probed wires without any knowledge on the secrets. In their paper, Ishai et al. propose a scheme, the so-called ISW scheme, to compile a circuit into a new randomized circuit (i.e. a circuit featuring random generation gates) which is resistant to t-probing attacks. Their scheme used some additive secret sharing (a.k.a. Boolean masking) of the processed variables. Specifically, each variable x is split into  $n \ge 2$  variables  $x_1, x_2, \ldots, x_n$ , called the shares, which are uniformly distributed among n-tuples satisfying  $x = x_1 + x_2 + \cdots + x_n$  (where + is the addition on  $\mathbb{F}_2$  in the original scheme).

Using such an additive sharing to protect a cryptographic computation was already proposed in 1999 as a protection against side-channel attacks [CJRR99, GP99]. Many masking schemes describing efficient implementations of ciphers protected at some given (low) orders were published in the early 2000's, see e.g. [Mes01, AG01, OMPR05]. In this context, the probing security notion is analogous to the security against so-called higher-order side-channel attacks. In such an attack, an adversary uses t leakage points from a power consumption trace (or electromagnetic trace) to extract information on the secret. If properly implemented, a t-probing secure scheme achieves provable security against this kind of attacks. The ISW scheme had hence a strong impact on the side-channel research community and it was used as a building block in many popular masking schemes, see e.g. [RP10, KHL11, CGP+12, CRV14, Cor14, RBN+15, WVGX15, GR17, BBP+16, BBP+17, JS17].

Although an ISW-based masking scheme can achieve some level of resistance against side-channel attacks, the probing security notion is not fully satisfactory in this context. In practice a side-channel adversary gets some leakage on the full computation and has no reason to limit herself to t leakage points. Nevertheless, the side-channel leakage is often (or can be made) noisy and the noise is known to be amplified by the masking order [CJRR99]. This was the motivation behind the formal noisy leakage model introduced by Prouff and Rivain in [PR13]. In this model, every variable (or wire) x in the computation leaks a noisy function f(x). The noisy property is captured by assuming that the bias introduced in the distribution of x by an observation of f(x) is smaller than some bound  $\delta$ .

Subsequently, Duc, Dziembowski and Faust showed that the security in the noisy leakage model could be obtained for a probing-secure scheme through a security reduction [DDF14]. In a nutshell, the so-called DDF reduction considers an intermediate leakage model called the random-probing model, which was already considered by Ishai et al. in [ISW03] and formalized by Ajtai in [Ajt11], in which each variable (or wire) is leaked to the adversary with a given probability p. By applying the Chernoff bound, one gets that a t-probing secure circuit  $\hat{C}$  is also p-random probing secure with  $p = O(t/|\hat{C}|)$  (where  $|\hat{C}|$  denotes the number of wires of  $\hat{C}$ ). Duc et al. could then show a transition from the p-random probing security to the  $\delta$ -noisy leakage security with  $\delta = O(p/|\mathbb{K}|)$  where  $|\mathbb{K}|$  is the base field of the computation. It was recently shown that the impact of the field size can be relaxed by refining the granularity of the computation [GJR18] or considering alternative definitions of the noisy leakage model [PGMP19].

The DFF reduction and the obtained security in the noisy leakage model is thus mainly impacted by the leakage rate (or probing rate) which is the ratio between the number of tolerated probes and the size of the circuit [ADF16]. In order to tolerate a significant leakage parameter  $\delta = O(t/|\hat{C}|)$ , the leakage rate should be as close as possible to 1. In

particular, one should be able to tolerate a number of probes that grows linearly with the circuit. To this aim, the circuit should achieve the stronger notion of region probing security formalized by Andrychowicz, Dziembowski, and Faust in [ADF16], namely it should be separable into regions that each tolerate some amount of probes independently of the total size of the circuit. This notion was already considered in the work of Ishai et al. and their scheme was shown to be region probing secure. Specifically, it can tolerate up to t < n/2 probes per protected gate, or gadget, for a masking order n. Since the ISW gadgets require  $O(n^2)$  operations, the obtained leakage rate is of O(1/n). Such a leakage rate is not fully satisfactory since it implies that the leakage noise should decrease linearly with the number of shares. In particular, no security can be obtained for the ISW gadgets in the context of a constant leakage rate (i.e. on a given target device) and some practical attacks were exhibited to underline this issue [BCPZ16a].

Fortunately, some schemes are known that achieve constant (or quasi-constant) leakage rates. Such a scheme was first proposed by Ajtai in [Ajt11] which achieves random probing security with leakage rate O(1). Another scheme, partly based on Ajtai's work, was proposed by Andrychowicz, Dziembowski, and Faust in [ADF16] which achieves probing security with leakage rate  $O(1/\log n)$ , and random-probing security with leakage rate O(1). More recently, Ananth, Ishai and Sahai [AIS18] have proposed a conceptually simpler approach to achieve random-probing security with leakage rate O(1). This approach has been further improved by Belaïd, Coron, Prouff, Rivain and Taleb in [BCP<sup>+</sup>20]. In terms of complexity, all these proposals imply a size of the protected circuit of  $O(|C|n^2)$  or larger, where |C| is the size of the original circuit. This was recently improved by Goudarzi, Joux and Rivain who proposed a scheme making use of a Fast Fourier Transform-based (FFT) polynomial multiplication to obtain the first construction achieving a  $O(|C|n \log n)$ complexity with a  $O(1/\log n)$  leakage rate. Unfortunately, their security proof has a flaw that we exhibit in this paper. Moreover, their scheme is restricted to working on base fields including the nth powers of unity, which notably excludes fields of characteristic 2 that are yet essential in some cryptographic primitives (such as the AES block cipher).

In [BBD<sup>+</sup>16], Barthe, Belaïd, Dupressoir, Fouque, Grégoire, Strub and Zucchini formalized the notion of composable quadqets which notably allows to prove region probing security. More precisely, they introduced the notion of Strong Non-Interference (SNI) which refines the notion of probing security, by separating between external and internal probes in the circuits. SNI security allows composing masked gadgets since the notion implies that gadgets stop the propagation of dependencies. However, compared to classical probing-secure gadgets, SNI gadgets are usually less efficient than probing-secure ones and require more randomness. Another approach consists in composing SNI gadgets and NI gadgets (a relaxation of the SNI notion) in a careful way to achieve security with better performances (see [BGR18] and references therein). In [CS20], Cassiers and Standaert introduced the notion of Probe Isolating Non-Interference (PINI) that allows secure composition and efficient implementations. It relies on the position of probes in a target implementation. Thanks to this notion, linear functions are directly composable and do not require to be refreshed and non-linear operations remain efficient. A circuit achieves PINI-security (and is consequently probing secure) if all its gadgets are PINI but the notion is not sufficient to achieve region-probing security.

In this paper, we introduce a new composition framework to construct circuits (or masked implementations) satisfying the region probing security notion. For this purpose, we formalize the property of *input-output separation* (IOS) for a refresh gadget and we show that it allows to simply construct region probing circuits from (weaker) probing secure gadgets and in particular more efficient gadgets which are only proven probing-secure but not SNI, e.g. [GJR18, BBP<sup>+</sup>16]. We show that this notion can be obtained from uniform SNI or PINI refresh gadgets but also with a simpler design, namely a variant of the refreshing algorithm due to Battistello, Coron, Prouff and Zeitoun [BCPZ16b]. It is

worth mentioning that the original refreshing gadget from [BCPZ16b] was proven SNI but for our purposes, we simplify and extend it and show that it achieves our new IOS security notion. The proposed variant can be used to refresh any kind of linear sharing with a quasilinear complexity  $\Theta(n \log n)$  and a  $O(1/\log n)$  leakage rate (for an *n*-size sharing).

We then revisit the quasilinear masking scheme of Goudarzi, Joux and Rivain [GJR18] (which we shall call the GJR scheme hereafter). This scheme is based on a polynomial sharing of the form  $a = \sum_{i} a_{i}\omega^{i}$ , where a is the plain variable and the  $a_{i}$ 's are the corresponding shares, and it uses an FFT-based polynomial multiplication to achieve a quasilinear complexity. We describe an improved version of the GJR scheme which works on any base field, including binary fields, and which relies on our composition framework. We further patch a flaw in the original security proof and extend it from the random probing model to the stronger region probing model. Specifically, our improved GJR scheme is secure in the region probing model provided that the underlying FFT algorithm is probing secure. From this ground, we obtain a probing-secure FFT using the approach of [GJR18], that is by relying on a large field  $|\mathbb{F}| = \Theta(2^{\lambda})$  and taking  $\omega$  at random. We hence get a region-probing-secure scheme for large fields. For smaller fields, our result is essentially a security reduction from the region probing security of the full scheme to the probing security of the FFT. Finally, we present an application of our extended GJR scheme and compare it with a more standard scheme based on SNI gadgets for two different ciphers: the Advanced Encryption Standard (AES) [AES01] and MiMC [AGR+16]: a cipher with efficient arithmetic representation on a large field. We show that this masking scheme significantly improves the efficiency of the masked cipher for a masking order  $n \ge 64$  for MiMC and  $n \ge 512$  for the AES. For the AES instantiation, we present a variant of Gao-Mateer additive FFT [GM10] with improved efficiency and which may be of independent interest.

# 2 Background on Probing Secure Circuits

#### 2.1 Notations

In this paper,  $\mathbb{K}$  shall denote a finite field. Vectors shall be denoted with bold letters, e.g. x. For any two random variables (or random vectors) X and Y, we shall write  $X \stackrel{\mathrm{id}}{=} Y$  whenever X and Y are identically distributed. For some positive integer  $n \in \mathbb{N}$ , we denote by [n] the set  $\{1, 2, \ldots, n\}$ . For any two vectors  $\mathbf{u}, \mathbf{v} \in \mathbb{K}^n$ ,  $\langle \mathbf{u}, \mathbf{v} \rangle$  denotes their inner product. For any finite set I, we denote by |I| the cardinality of I. Let  $I \subseteq [n]$  and  $\mathbf{v} = (v_1, \ldots, v_n) \in \mathbb{K}^n$ , we denote by  $\mathbf{v}_{|I|}$  the |I|-tuple  $(v_i)_{i \in I}$ . We shall denote  $x \leftarrow \mathcal{X}$  the action of picking x uniformly at random in some set  $\mathcal{X}$ , and  $y \leftarrow \mathcal{A}(x)$  the action of defining y as the output of an algorithm  $\mathcal{A}$  on input x. If  $\mathcal{A}$  is a probabilistic algorithm, then  $y \leftarrow \mathcal{A}(x)$  is a random assignment of y on input x and for a uniform random tape.

#### 2.2 Basic Definitions

**Arithmetic circuits.** Given a finite field  $\mathbb{K}$ , an *arithmetic circuit* is a circuit processing elements of  $\mathbb{K}$  through simple arithmetic operations. Formally, it is modeled as a directed acyclic graph whose vertices are *gates* that belong to the following types:

- input gate (fan-in 0, fan-out 1) which holds an input value of the circuit,

- output gate (fan-in 1, fan-out 0) which receives an output value of the circuit,

- constant gate (fan-in 0, fan-out 1) which outputs a constant value of K,

- addition gate (fan-in 2, fan-out 1) which outputs the sum (on  $\mathbb{K}$ ) of the two input values,

- subtraction gate (fan-in 2, fan-out 1) which outputs the difference (on  $\mathbb{K}$ ) of the two input values,

- multiplication gate (fan-in 2, fan-out 1) which outputs the product (on  $\mathbb{K}$ ) of the two input values,

- copy gate (fan-in 1, fan-out 2) which outputs two copies of the input.

The addition, subtraction and multiplication gates are further called *operation gates*. The edges of an arithmetic circuit are called the *wires*. A *randomized arithmetic circuit* is a arithmetic circuit augmented with a

- random gate (fan-in 0, fan-out 1) which outputs a fresh uniform random value of  $\mathbb{K}$ . Given some assignment of the input gates, all the wires of a circuit can be assigned subsequently following the input-output behavior of the gates, which finally leads to an assignment of the output gates. For an arithmetic circuit C with n input gates and m output gates, we denote  $\mathbf{y} = C(\mathbf{x}) \in \mathbb{K}^m$  the output of C (i.e. the assignment of the output gates of C) on input  $\mathbf{x} \in \mathbb{K}^n$  (i.e. when the input gates are assigned to  $\mathbf{x}$ ). For a randomized arithmetic circuit C with q random gates, we denote  $\mathbf{y} = C^{\rho}(\mathbf{x})$  the output of C on input  $\mathbf{x}$  and such that each random gate outputs a coordinate of  $\rho \in \mathbb{K}^q$ . The parameter  $\rho$  is then called the random tape of C. Whenever  $\rho$  is omitted,  $\mathbf{y} = C(\mathbf{x})$  denotes the random vector obtained for a uniform distribution of  $\rho$ .

Let C be a randomized arithmetic circuit with n input gates, m output gates, q random gates, and let consider that the wires of C are labeled from 1 to s (where s is the total number of wires in C). Then for any set  $\mathcal{W} \subseteq [s]$  with  $|\mathcal{W}| = t$ , we shall denote by  $C_{\mathcal{W}}^{\boldsymbol{\rho}}(\boldsymbol{x}) \in \mathbb{K}^t$  the tuple composed of the assignments of the wires with labels in  $\mathcal{W}$  on input  $\boldsymbol{x} \in \mathbb{K}^n$  and random tape  $\boldsymbol{\rho} \in \mathbb{K}^q$ . In particular, each coordinate of  $C_{\mathcal{W}}^{\boldsymbol{\rho}}(\boldsymbol{x})$  is a deterministic function of  $\boldsymbol{x}$  and  $\boldsymbol{\rho}$ . Here again, whenever  $\boldsymbol{\rho}$  is omitted,  $C_{\mathcal{W}}(\boldsymbol{x})$  denotes the random vector obtained for a uniform distribution of  $\boldsymbol{\rho}$  on  $\mathbb{K}^q$ .

**Circuit compilers.** We now recall the definition of *circuit compilers* as formalized in [AIS18] (but adapted to arithmetic circuits). We shall call a  $\mathbb{K}$ -string any tuple of elements from the base field  $\mathbb{K}$ .

**Definition 1** (Circuit Compiler). A circuit compiler is a triplet of algorithms (Compile, Encode, Decode) defined as follows:

- Compile (circuit compilation) is a deterministic algorithm that takes as input an arithmetic circuit C and outputs a randomized arithmetic circuit  $\widehat{C}$ .

- Encode (input encoding) is a probabilistic algorithm that takes as input a  $\mathbb{K}$ -string  $\hat{x}$  and outputs a  $\mathbb{K}$ -string  $\hat{x}$ .

- Decode (output decoding) is a deterministic algorithm that takes as input a  $\mathbb{K}$ -string  $\hat{y}$  and outputs a  $\mathbb{K}$ -string y.

These three algorithms satisfy the following properties:

• Correctness: For every arithmetic circuit C of input length  $\ell$ , and for every  $x \in \mathbb{K}^{\ell}$ , we have

$$\Pr\left(\mathsf{Decode}\big(\widehat{C}(\widehat{\boldsymbol{x}})\big) = C(\boldsymbol{x}) \ \middle| \ \widehat{\boldsymbol{x}} \leftarrow \mathsf{Encode}(\boldsymbol{x})\right) = 1 \ ,$$

where  $\widehat{C} = \mathsf{Compile}(C)$ .

• Efficiency: For some parameter called the encoding order  $n \in \mathbb{N}$ , the running time of  $\mathsf{Compile}(C)$  is  $\mathsf{poly}(n,|C|)$ , the running time of  $\mathsf{Encode}(\boldsymbol{x})$  is  $\mathsf{poly}(n,|\boldsymbol{x}|)$  and the running time of  $\mathsf{Decode}(\widehat{\boldsymbol{y}})$  is  $\mathsf{poly}(n,|\widehat{\boldsymbol{y}}|)$ , where  $\mathsf{poly}(n,q) = O(n^{k_1}q^{k_2})$  for some constants  $k_1, k_2$ .

Sharings and gadgets. Let  $n \in \mathbb{N}$  and let  $\mathbf{v} \in (\mathbb{K}^*)^n$ . A  $\mathbf{v}$ -linear sharing of  $x \in \mathbb{K}$  is a vector  $\mathbf{x} \in \mathbb{K}^n$  such that  $\langle \mathbf{v}, \mathbf{x} \rangle = x$ . The coordinates of a linear sharing  $\mathbf{x} \in \mathbb{K}^n$  are called the shares of  $\mathbf{x}$ . A random vector  $\mathbf{x}$  is a uniform  $\mathbf{v}$ -linear sharing of  $\mathbf{x}$  if  $\langle \mathbf{v}, \mathbf{x} \rangle = x$  and  $\mathbf{x}_{|I|}$  is uniformly distributed over  $\mathbb{K}^t$  for any  $I \subset [n]$  with |I| < n.

Let v-Enc denote a probabilistic algorithm that on input x outputs a uniform v-linear sharing of x. For instance v-Enc(x) performs the following:

$$x_1 \leftarrow \mathbb{K}; \ x_2 \leftarrow \mathbb{K}; \ \cdots \ x_{n-1} \leftarrow \mathbb{K};$$

$x_n \leftarrow v_n^{-1} (x - \langle \boldsymbol{v}, (x_1, \dots, x_{n-1}, 0) \rangle)$

and returns the vector  $\mathbf{x} = (x_1, x_2, \dots, x_n)$ . We further denote  $\mathbf{v}$ -Dec the deterministic algorithm that on input of a  $\mathbf{v}$ -linear sharing of x outputs x. This algorithm simply computes the inner product  $\mathbf{v}$ -Dec $(\mathbf{x}) = \langle \mathbf{v}, \mathbf{x} \rangle$ .

For any operation  $g:(x,y)\in\mathbb{K}^2\mapsto z\in\mathbb{K}$  and for any vector  $\boldsymbol{v}\in\mathbb{K}^n$ , a  $\boldsymbol{v}$ -gadget of g is a randomized arithmetic circuit with 2n input gates and n output gates, which, on input of a  $\boldsymbol{v}$ -linear sharing of x and a  $\boldsymbol{v}$ -linear sharing of y, outputs a  $\boldsymbol{v}$ -linear sharing of z=g(x,y), for any  $x,y\in\mathbb{K}$ . In particular, G is a  $\boldsymbol{v}$ -gadget of g if and only if for every random tape  $\boldsymbol{\rho}$ ,  $\boldsymbol{v}$ -Dec $(G^{\boldsymbol{\rho}}(\boldsymbol{x},\boldsymbol{y}))=g(x,y)$ . A  $\boldsymbol{v}$ -refresh gadget is a randomized arithmetic circuit with n input gates and n output gates, which, on input of a  $\boldsymbol{v}$ -linear sharing of x outputs a  $\boldsymbol{v}$ -linear sharing of x, for any  $x\in\mathbb{K}$ .

**Standard circuit compilers.** Consider a family of vectors  $\mathcal{V} = \{\boldsymbol{v}_n \in \mathbb{K}^n\}_{n \in \mathbb{N}}$  and three families of gadgets  $\mathcal{G}^{\oplus} = \{G_n^{\oplus}\}_{n \in \mathbb{N}}$ ,  $\mathcal{G}^{\otimes} = \{G_n^{\otimes}\}_{n \in \mathbb{N}}$  and  $\mathcal{G}^{\mathsf{R}} = \{G_n^{\mathsf{R}}\}_{n \in \mathbb{N}}$  such that for every  $n \in \mathbb{N}$ ,  $G_n^{\oplus}$  is a  $\boldsymbol{v}_n$ -gadget for the addition on  $\mathbb{K}$ ,  $G_n^{\otimes}$  is a  $\boldsymbol{v}_n$ -gadget for the multiplication on  $\mathbb{K}$ , and  $G_n^{\mathsf{R}}$  is a  $\boldsymbol{v}_n$ -refresh gadget.

The standard circuit compiler for  $(\mathcal{V}, \mathcal{G}^{\oplus}, \mathcal{G}^{\otimes}, \mathcal{G}^{\mathsf{R}})$  with encoding order n is the circuit compiler for which

- Encode applies  $v_n$ -Enc to each coordinate of the input K-string;

- Decode applies  $v_n$ -Dec to each coordinate of the input K-string;

- Compile takes an arithmetic circuit C and outputs the randomized arithmetic circuit  $\widehat{C}$  such that each addition gate is replaced by an addition gadget  $G_n^{\oplus}$  followed by a refresh gadget  $G_n^{\mathsf{R}}$ , each multiplication gate is replaced by a multiplication gadget  $G_n^{\otimes}$  followed by a refresh gadget  $G_n^{\mathsf{R}}$ , each constant gate outputting  $\alpha$  is replaced by n constant gates with constants  $(\alpha \cdot v_1^{-1}, 0, \ldots, 0)$  followed by a refresh gadget  $G_n^{\mathsf{R}}$  and each copy gate is replaced by a copy of the input sharing (through n copy gates) followed by a refresh gadget  $G_n^{\mathsf{R}}$  per output sharing.

It is not hard to see that such a circuit compiler achieves correctness and efficiency, provided, for the latter, that the sizes of the gadgets  $G_n^{\oplus}$ ,  $G_n^{\otimes}$  and  $G_n^{\mathsf{R}}$  are polynomial in n.

To ease the presentation, we restrict the notion of standard circuit compiler to three types of gadgets (addition, multiplication and refresh) but in practice we consider compilers for which the addition gadget is replaced by a broader class of *sharewise* gadgets. These gadgets apply a linear operation (addition, subtraction, multiplication by a constant, or any  $\mathbb{F}_0$ -linear operation if  $\mathbb{F}$  is an  $\mathbb{F}_0$ -module) sharewisely to the input linear sharing(s).

#### 2.3 Probing Security

Throughout the paper, the notion of *simulator* will refer to a polynomial-time probabilistic algorithm. We will say that a random vector  $\boldsymbol{w}$  can be *perfectly simulated* (possibly given some input  $\boldsymbol{in}$ ) if there exists a simulator  $\mathcal{S}$  that (given  $\boldsymbol{in}$ ) outputs a vector which is identically distributed as  $\boldsymbol{w}$  (over the internal randomness of the simulator), which shall be denoted  $\mathcal{S}(\boldsymbol{in}) \stackrel{\mathrm{id}}{=} \boldsymbol{w}$ .

Informally speaking, a randomized arithmetic circuit achieves t-probing security, if leaking the value of t arbitrary wires (i.e. allowing t probes on the circuit) does not reveal any information about the input (provided that the latter has been properly encoded). This is formally define hereafter.

**Definition 2** (Probing Security). A randomized arithmetic circuit  $\widehat{C}$  is *t-probing secure* w.r.t. an encoding algorithm Encode if for every plain input  $\boldsymbol{x}$  and for every set  $\mathcal{W} \subseteq [|\widehat{C}|]$ , with  $|\mathcal{W}| \leq t$ , there exists a simulator  $\mathcal{S}_{\widehat{C},\mathcal{W}}$  such that

$$\mathcal{S}_{\widehat{C},\mathcal{W}}(\perp)\stackrel{\mathrm{id}}{=} \widehat{C}_{\mathcal{W}}(\mathsf{Encode}(oldsymbol{x}))$$

.

A circuit compiler (Compile, Encode, Decode) is said to achieve t-probing security if for every arithmetic circuit C, the randomized arithmetic circuit  $\widehat{C} = \mathsf{Compile}(C)$  is t-probing secure w.r.t. Encode. Note that factually, the parameter t is a function of the encoding order n. For instance, the first probing-secure scheme due to Ishai, Sahai and Wagner achieves t-probing security with  $t \leq (n-1)/2$  and an efficiency  $|\widehat{C}| = \Theta(n^2|C|)$ .

Most probing-secure circuit compilers are based on the composition of gadgets. These gadgets are themselves probing-secure w.r.t. the underlying encoding scheme but they must also satisfy composition properties so that the overall compiled circuit is probing secure. In particular, the notions of (strong) non-interference, or (S)NI and probe isolating non-interference, or PINI have been proposed and studied in [BBD+16, BGR18, BBD+18, CS20]. In this paper, we introduce another notion called input-output separation (see Section 3) which is aimed to enable the composition for a stronger notion of probing security, namely the region probing security. In a nutshell, a circuit is region probing secure if it is composed of several sub-circuits (e.g. several gadgets) that can each tolerate some constant amount of probes (irrespective of the total number of sub-circuits). We shall then consider the probing rate (or leakage rate) of such a circuit as the maximum ratio between the number of tolerable probes over the size of a sub-circuit. Region probing security is formalized hereafter.

Let us first introduce the notion of circuit partition. For any (randomized) arithmetic circuit C, we call  $C \equiv (C_1, C_2, \ldots, C_m)$  a circuit partition where each  $C_i$  is a sub-circuit of C such that the gates of the  $C_i$ 's form a partition of the gates of C. We further denote by  $W_{C_i}$  the set of wires with source gate in  $C_i$ , so that  $W_{C_1}, \ldots, W_{C_m}$  is a partition of [|C|].

**Definition 3** (Region Probing Security). A randomized circuit  $\widehat{C}$  is r-region probing secure (i.e. with probing rate r) w.r.t. an encoding algorithm Encode if there exists a circuit partition  $\widehat{C} \equiv (C_1, C_2, \dots, C_m)$  such that for every plain input  $\boldsymbol{x}$  and for every set  $W_1 \subseteq W_{C_1}, W_2 \subseteq W_{C_2}, \dots, W_m \subseteq W_{C_m}$ , with  $|W_i| \leq \lceil r|C_i| \rceil$ , there exists a simulator  $\mathcal{S}_{\widehat{C}|W}$  such that

$$\mathcal{S}_{\widehat{C}|\mathcal{W}}(\perp) \stackrel{\mathrm{id}}{=} \widehat{C}_{\mathcal{W}}(\mathsf{Encode}(\boldsymbol{x})) \ ,$$

where  $W = W_1 \cup W_2 \cup \ldots \cup W_m$ . A circuit compiler (Compile, Encode, Decode) is r-region probing secure if for every circuit C the compiled circuit  $\widehat{C} = \mathsf{Compile}(C)$  is r-region probing secure w.r.t. Encode (where r might be a function of the encoding order and the circuit size).

We shall further say that a circuit  $\widehat{C}$  is  $(r, \varepsilon)$ -region probing secure (i.e. with probing rate r and simulation failure  $\varepsilon$ ), if the simulator fails (i.e. returns  $\bot$ ) with probability

$$\Pr\left(\mathcal{S}_{\widehat{C},\mathcal{W}}(\bot) = \bot\right) \leq m \cdot \varepsilon$$

,

(m being the number of regions) and returns a perfect simulation otherwise:

$$\left(\mathcal{S}_{\widehat{C},\mathcal{W}}(\bot)\mid\mathcal{S}_{\widehat{C},\mathcal{W}}(\bot)\neq\bot\right)\stackrel{\mathrm{id}}{=}\widehat{C}_{\mathcal{W}}(\mathsf{Encode}(\boldsymbol{x}))\ .$$

The region probing security is a relevant security property for a cryptographic implementation while considering side-channel attacks. Indeed, security in the so-called *noisy leakage model* which captures the physical reality of power and electromagnetic side-channel leakages can be reduced to region probing security. These notions and reductions are recalled in Appendix B.

### 3 Composability from Input-Output Separation

#### 3.1 Input-Output Separation

We introduce hereafter the *input-output separation* security notion for a refresh gadget. Such a property has originally been used in the GJR scheme to achieve composition in the random probing model [GJR18]. We formalize this notion hereafter as general composition property to achieve region probing security. For the sake of simplicity, the definition given in this section only considers refresh gadgets but it can be generalized to any kind of gadgets (see Appendix A for a general definition).

We first introduce the notion of uniformity for a gadget which will be a requirement for our new security notion.

**Definition 4** (Uniformity). Let  $\mathbf{v} \in (\mathbb{K}^*)^n$ . A  $\mathbf{v}$ -refresh gadget G is uniform, if for every  $\mathbf{x} \in \mathbb{K}^n$ , the output  $G(\mathbf{x})$  is a uniform  $\mathbf{v}$ -linear sharing of  $\langle \mathbf{v}, \mathbf{x} \rangle$ .

In the following, we shall say that a pair of vector  $(\boldsymbol{x}, \boldsymbol{y}) \in (\mathbb{K}^n)^2$  is admissible for a gadget G if there exists a random tape  $\boldsymbol{\rho}$  such that  $\boldsymbol{y} = G^{\boldsymbol{\rho}}(\boldsymbol{x})$ . For an admissible pair  $(\boldsymbol{x}, \boldsymbol{y})$  and a set  $\mathcal{W} \subseteq [|G|]$ , the wire distribution of G in  $\mathcal{W}$  induced by  $(\boldsymbol{x}, \boldsymbol{y})$ , denoted  $G_{\mathcal{W}}(\boldsymbol{x}, \boldsymbol{y})$ , is the random vector  $G_{\mathcal{W}}^{\boldsymbol{\rho}}(\boldsymbol{x})$ , i.e. the tuple of wire values for the wire indexes in  $\mathcal{W}$ , obtained for a uniform drawing of  $\boldsymbol{\rho}$  among the set  $\{\boldsymbol{\rho} \in \mathbb{K}^q : G_{\mathcal{W}}^{\boldsymbol{\rho}}(\boldsymbol{x}) = \boldsymbol{y}\}$ .

**Definition 5** (IOS). Let  $\mathbf{v} \in (\mathbb{K}^*)^n$  and let G be a  $\mathbf{v}$ -refresh gadget with s wires. G is said t-input-output separative (t-IOS), if it is uniform and if for every admissible pair  $(\mathbf{x}, \mathbf{y})$  and every set of wires  $\mathcal{W} \subseteq [s]$  with  $|\mathcal{W}| \le t$ , there exists a (two-stage) simulator  $S_{G,\mathcal{W}} = (S_{G,\mathcal{W}}^{(1)}, S_{G,\mathcal{W}}^{(2)})$  such that

1.

$$\mathcal{S}_{G,\mathcal{W}}^{(1)}(\perp) = (\mathcal{I},\mathcal{J})$$

where  $\mathcal{I},\mathcal{J} \subseteq [n]$ , with  $|\mathcal{I}| \leq |\mathcal{W}|$  and  $|\mathcal{J}| \leq |\mathcal{W}|$ ;

2.

$$\mathcal{S}_{G,\mathcal{W}}^{(2)}(\boldsymbol{x}_{|\mathcal{I}},\boldsymbol{y}_{|\mathcal{J}}) \stackrel{\mathrm{id}}{=} G_{\mathcal{W}}(\boldsymbol{x},\boldsymbol{y}).$$

A v-refresh gadget is simply said to be IOS if it is n-IOS.

The above definition generalizes the notion of *input-output linear separability* used in the GJR scheme [GJR18]. Our definition has two differences with the GJR notion:

- the GJR notion requires a deterministic (functional) relation between the probed wires and the input/output shares whereas we only require the ability of simulating the probed wires from some input/output shares;

- the GJR notion requires the knowledge of arbitrary linear combinations of the input/output shares whereas we require the knowledge of some input/output shares. The first difference makes our definition easier to achieve without impacting the composability. Indeed, in any probing security context, the ability of achieving a perfect simulation is sufficient to prove the security. The second difference makes our definition harder to achieve but more useful to different composition contexts (where the probing security might not rely on linear algebra). Moreover, we describe in Section 4 a refresh gadget achieving our version of input-output separation.

The intuition behind the IOS notion can be understood as follows. Any probing leakage from an IOS refresh gadget can be simulated given a subset of its input shares and output shares. We can therefore reduce the standard region probing security game to a game in which the refresh gadget does not leak anything but its surrounding gadgets leak more. The uniformity property then implies that the leakages from two gadgets separated by a refresh gadget are mutually independent. One can then achieve a perfect simulation of the full leakage through independent simulations of the *separated* leakages from the two gadgets.

<sup>&</sup>lt;sup>1</sup>A set of shares being a particular case of a set of linear combinations of shares.

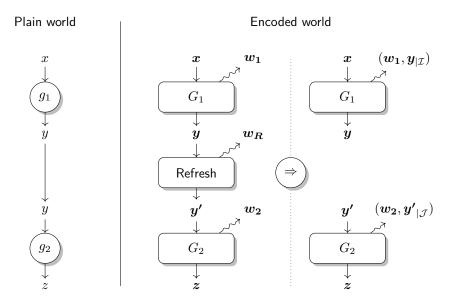

Figure 1: Illustration of the IOS property.

This is illustrated on Figure 1. The full probing leakage  $(\boldsymbol{w}_1, \boldsymbol{w}_R, \boldsymbol{w}_2)$  can be simulated from  $(\boldsymbol{w}_1, \boldsymbol{y}_{|\mathcal{J}}, \boldsymbol{w}_2)$ . Moreover, the refresh uniformity implies that, given x, the separated leakages  $(\boldsymbol{w}_1, \boldsymbol{y}_{|\mathcal{J}})$  and  $(\boldsymbol{w}_2, \boldsymbol{y}'_{|\mathcal{J}})$  are mutually independent. Therefore, if one can simulate  $(\boldsymbol{w}_1, \boldsymbol{y}_{|\mathcal{I}})$  on the one hand and  $(\boldsymbol{w}_2, \boldsymbol{y}'_{|\mathcal{J}})$  on the other hand, then one can simulate the full leakage.

#### 3.2 Composition Theorem

We now provide a formal proof of composition based on the IOS property defined above. Specifically, we show that a standard circuit compiler interleaving operation gadgets and refresh gadgets is region probing secure provided that its operation gadgets are probing secure, and its refresh gadgets are IOS.

As introduced in Section 2, we consider hereafter a family of vectors  $\mathcal{V} = \{v_n \in \mathbb{K}^n\}_{n \in \mathbb{N}}$  and three families of gadgets  $\mathcal{G}^{\oplus} = \{G_n^{\oplus}\}_{n \in \mathbb{N}}$ ,  $\mathcal{G}^{\otimes} = \{G_n^{\otimes}\}_{n \in \mathbb{N}}$  and  $\mathcal{G}^{\mathsf{R}} = \{G_n^{\mathsf{R}}\}_{n \in \mathbb{N}}$  such that for every  $n \in \mathbb{N}$ ,  $G_n^{\oplus}$  is a  $v_n$ -gadget for the addition on  $\mathbb{K}$ ,  $G_n^{\otimes}$  is a  $v_n$ -gadget for the multiplication on  $\mathbb{K}$ , and  $G_n^{\mathsf{R}}$  is a  $v_n$ -refresh gadget. The following theorem gives our composition result for the standard circuit compiler for  $(\mathcal{V}, \mathcal{G}^{\oplus}, \mathcal{G}^{\otimes}, \mathcal{G}^{\mathsf{R}})$ .

**Theorem 1.** If for every  $n \in \mathbb{N}$ ,

- $G_n^{\oplus}$  is  $t_n^{\oplus}$ -probing secure (w.r.t.  $v_n$ -Enc),

- $G_n^{\otimes}$  is  $t_n^{\otimes}$ -probing secure (w.r.t.  $v_n$ -Enc),

- $G^{\mathsf{R}_n}$  is  $t_n^{\mathsf{R}}$ -IOS.

then the standard circuit compiler for  $(\mathcal{V}, \mathcal{G}^{\oplus}, \mathcal{G}^{\otimes}, \mathcal{G}^{\mathsf{R}})$  is  $r_n$ -region probing secure with

$$r_n = \max_{t \le t_n^R} \min\left(\frac{t_n^{\oplus} - 3t}{|G_n^{\oplus}|}, \frac{t_n^{\otimes} - 3t}{|G_n^{\otimes}|}, \frac{t}{|G_n^{\mathsf{R}}|}\right). \tag{1}$$

*Proof.* Let  $n \in \mathbb{N}$  and let  $t \leq t_n^{\mathsf{R}}$ . Let C be an arithmetic circuit composed of m operation gates, and let  $\widehat{C}$  be the randomized arithmetic circuit obtained by calling the standard

circuit compiler for  $(\mathcal{V}, \mathcal{G}^{\oplus}, \mathcal{G}^{\otimes}, \mathcal{G}^{\mathsf{R}})$  on C. We shall denote by  $G_1, G_2, \ldots, G_m$  the operation gadgets of  $\widehat{C}$  and by  $G_1^{\mathsf{R}}, G_2^{\mathsf{R}}, \ldots, G_m^{\mathsf{R}}$  the refresh gadgets of  $\widehat{C}$  where  $G_i^{\mathsf{R}}$  is placed in output of  $G_i$  for every i. We further denote by  $\mathcal{W}_{G_i}$  and  $\mathcal{W}_{G_i^{\mathsf{R}}}$  the set of wires with source gate in  $G_i$  and  $G_i^{\mathsf{R}}$  respectively. Finally, we denote  $t_i$  the integer such that  $t_i = t_n^{\oplus} - 3t$  if  $G_i = G_n^{\oplus}$  and  $t_i = t_n^{\otimes} - 3t$  otherwise (i.e. if  $G_i = G_n^{\otimes}$ ) for  $i \in \{1, \ldots, m\}$ . Let

$$\mathcal{W} = \bigcup_{i=1}^{m} \mathcal{W}_{i} \cup \bigcup_{i=1}^{m} \mathcal{W}_{i}^{\mathsf{R}} \subseteq [|\widehat{C}|]$$

where  $W_i \subseteq W_{G_i}$ , with  $W_i \leq t_i$ , and  $W_i^{\mathsf{R}} \subseteq W_{G_i^{\mathsf{R}}}$ , with  $W_i^{\mathsf{R}} \leq t$  for every  $i \in [m]$ . We will show that for any input in of C, there exists a simulator  $\mathcal{S}_{\widehat{C}|\mathcal{W}}$  such that

$$\mathcal{S}_{\widehat{C},\mathcal{W}}(\perp) \stackrel{\mathrm{id}}{=} \widehat{C}_{\mathcal{W}}(\mathsf{Encode}(\boldsymbol{in})) \ ,$$

which directly implies the  $r_n$ -region probing security of the standard circuit compiler with

$$r_n = \min\left(\frac{t_n^{\oplus} - 3t}{|G_n^{\oplus}|}, \frac{t_n^{\otimes} - 3t}{|G_n^{\otimes}|}, \frac{t}{|G_n^{\mathsf{R}}|}\right).$$

The above shall hold for every  $t \leq t_n^{\mathsf{R}}$  which yields the maximum in (1).

The simulator  $\mathcal{S}_{\widehat{C},\mathcal{W}}$  is simply obtained by running the simulators inherited from the probing security of the  $G_i$ 's and the IOS property of the  $G_i^R$ 's. Specifically:

• The IOS property of the  $G_i^R$ 's implies that, for every  $i \in [m]$ , there exists a (two-

- The IOS property of the  $G_i^{\mathbf{R}}$ 's implies that, for every  $i \in [m]$ , there exists a (two-stage) simulator  $\mathcal{S}_{G_i^{\mathbf{R}},\mathcal{W}_i^{\mathbf{R}}} = \left(\mathcal{S}_{G_i^{\mathbf{R}},\mathcal{W}_i^{\mathbf{R}}}^{(1)}, \mathcal{S}_{G_i^{\mathbf{R}},\mathcal{W}_i^{\mathbf{R}}}^{(2)}\right)$  such that for every  $(\boldsymbol{x},\boldsymbol{y}) \in \mathbb{K}^n \times \mathbb{K}^n$  admissible for  $G_i^{\mathbf{R}}$ :

- 1.  $\mathcal{S}^{(1)}_{G_i^R, \mathcal{W}_i^R}(\bot) = (\mathcal{I}, \mathcal{J}) \text{ where } \mathcal{I}, \mathcal{J} \subseteq [n], \text{ with } |\mathcal{I}| \leq |\mathcal{W}| \text{ and } |\mathcal{J}| \leq |\mathcal{W}|;$

- 2.  $\mathcal{S}^{(2)}_{G_i^R, \mathcal{W}_i^R}(\boldsymbol{x}_{|\mathcal{I}}, \boldsymbol{y}_{|\mathcal{J}})$  outputs a perfect simulation of  $\widehat{C}_{\mathcal{W}_i^R}(\mathsf{Encode}(\boldsymbol{in}))$  given that the pair of input/output sharings of  $G_i^R$  equals  $(\boldsymbol{x}, \boldsymbol{y})$ .

Here  $\boldsymbol{x}_{|\mathcal{I}}$  corresponds to  $|\mathcal{I}| \leq t$  (output) wires of the gadget  $G_i$  and  $\boldsymbol{y}_{|\mathcal{J}}$  corresponds to  $|\mathcal{J}| \leq t$  (input) wires of the gadget  $G_j$  subsequent to the refresh  $G_i^R$ . In particular, there exist two sets  $\mathcal{I}_i \subseteq \mathcal{W}_{G_i}$  and  $\mathcal{J}_i \subseteq \mathcal{W}_{G_j}$  such that

$$m{x}_{|\mathcal{I}} = \widehat{C}_{\mathcal{I}_i}(\mathsf{Encode}(m{in})) \ \ \mathrm{and} \ \ m{y}_{|\mathcal{J}} = \widehat{C}_{\mathcal{J}_i}(\mathsf{Encode}(m{in})) \ .$$

• Let  $\phi$  and  $\psi$  be the index-mapping functions such that the two input sharings of gadget  $G_i$  are output sharings of refresh gadgets  $G_{\phi(i)}^{\mathsf{R}}$  and  $G_{\psi(i)}^{\mathsf{R}}$ . By defining  $\overline{\mathcal{W}}_i := \mathcal{W}_i \cup \mathcal{I}_i \cup \mathcal{I}_{\phi(i)} \cup \mathcal{I}_{\psi(i)}$ , we get

$$\bigcup_{i=1}^m \overline{\mathcal{W}}_i = \bigcup_{i=1}^m \mathcal{W}_i \cup \bigcup_{i=1}^m \mathcal{I}_i \cup \bigcup_{i=1}^m \mathcal{J}_i \text{ with } \overline{\mathcal{W}}_i \subseteq \mathcal{W}_{G_i} \text{ and } |\overline{\mathcal{W}}_i| \le t_i + 3t .$$

• The probing security of the  $G_i$ 's implies that, for every  $i \in [m]$ , there exists a simulator  $\mathcal{S}_{G_i,\overline{\mathcal{W}}_i}$  such that

$$\mathcal{S}_{G_i,\overline{\mathcal{W}}_i}(\perp) \stackrel{\mathrm{id}}{=} \widehat{C}_{\overline{\mathcal{W}}_i}(\mathsf{Encode}(in))$$

.

We now have all the ingredients to describe the simulator  $\mathcal{S}_{\widehat{C},W}$ . It proceeds as follows:

- 1.  $\mathcal{S}_{\widehat{C},\mathcal{W}}$  first call the simulators  $\mathcal{S}_{G_i^R,\mathcal{W}_i^R}^{(1)}(\bot)$  to get the sets  $\mathcal{I}_i$ 's and  $\mathcal{J}_i$ 's. 2.  $\mathcal{S}_{\widehat{C},\mathcal{W}}$  then calls the simulators  $\mathcal{S}_{G_i,\overline{\mathcal{W}}_i}(\bot)$  to get tuples

$$\boldsymbol{z}_i = (\boldsymbol{w}_i, \boldsymbol{x}_i, \boldsymbol{y}_{\phi(i)}, \boldsymbol{y}_{\psi(i)}) \stackrel{\mathrm{id}}{=} \widehat{C}_{\overline{\mathcal{W}}_i}(\mathsf{Encode}(\boldsymbol{in})) \ ,$$

where  $w_i$ ,  $x_i$ ,  $y_{\phi(i)}$ ,  $y_{\psi(i)}$  corresponds to the indexes  $W_i$ ,  $\mathcal{I}_i$ ,  $\mathcal{I}_{\phi(i)}$  and  $\mathcal{I}_{\psi(i)}$  respectively. By the uniformity property of the refresh the distributions  $C_{\mathcal{W}_{G_i}}(\mathsf{Encode}(in))$ , given in, are mutually independent which implies

$$(oldsymbol{z}_1,oldsymbol{z}_2,\ldots,oldsymbol{z}_m)\stackrel{ ext{id}}{=} \widehat{C}_{igcup_i \overline{\mathcal{W}}_i}(\mathsf{Encode}(oldsymbol{in}))$$

.

3.  $\mathcal{S}_{\widehat{C},\mathcal{W}}$  finally calls the simulators  $\mathcal{S}_{G_i^R,\mathcal{W}_i^R}^{(2)}$  on inputs  $(\boldsymbol{x}_i,\boldsymbol{y}_i)$  to get tuples  $\boldsymbol{w}_i^R$  such

$$oldsymbol{w}_i^{\mathsf{R}} \stackrel{\mathrm{id}}{=} \widehat{C}_{\mathcal{W}_:^{\mathsf{R}}}(\mathsf{Encode}(oldsymbol{in})) \; ,$$

and outputs  $(\boldsymbol{w}_1, \boldsymbol{w}_1^{\mathsf{R}}, \dots, \boldsymbol{w}_m, \boldsymbol{w}_m^{\mathsf{R}})$  as simulation. The IOS property finally implies

$$\mathcal{S}_{\widehat{C},\mathcal{W}}(\bot) = (\boldsymbol{w}_1,\boldsymbol{w}_1^\mathsf{R},\dots,\boldsymbol{w}_m,\boldsymbol{w}_m^\mathsf{R}) \stackrel{\mathrm{id}}{=} \widehat{C}_{\mathcal{W}}(\mathsf{Encode}(\boldsymbol{in})) \;,$$

which concludes the proof.

#### 3.3 Comparison with Non-Interference Security Notions

It is well-known that composition of probing secure gadgets is not always probing secure [CPRR14]. Stronger security definitions were previously proposed to analyse the security of large circuits viewed as the composition of simple gadgets. The first such notion, (strong) non-interference, or (S)NI, was proposed in [BBD<sup>+</sup>16]. The notion of Probe Isolating Non-Interference (PINI) was also recently introduced in [CS20]. In this section, we compare our composition approach with the ones underlying the (S)NI and PINI notions and then show some implications between these notions and our IOS notion.

We first recall the (S)NI and PINI definitions while extending them from standard Boolean sharing to the general case of v-sharings. For a v-refresh gadget, the (S)NI notion is defined as follows:

**Definition 6** (NI and SNI). Let  $v \in (\mathbb{K}^*)^n$  and let G be a v-refresh gadget with s wires. G is said t-Non-Interferent (t-NI) (resp. t-Strong Non-Interferent (t-SNI)), if for every x and every set of internal wires  $\mathcal{W} \subseteq [s]$  with  $|\mathcal{W}| \le t_1$  and every set of output wires  $\mathcal{O} \subseteq [s]$  with  $|\mathcal{O}| \le t_2$  and  $t_1 + t_2 \le t$ , there exists a (two-stage) simulator  $\mathcal{S}_{G,\mathcal{W},\mathcal{O}} = (\mathcal{S}_{G,\mathcal{W},\mathcal{O}}^{(1)}, \mathcal{S}_{G,\mathcal{W},\mathcal{O}}^{(2)})$ such that

- 1.  $\mathcal{S}_{G,W,\mathcal{O}}^{(1)}(\perp) = \mathcal{I}$  where  $\mathcal{I} \subseteq [n]$ , with  $|\mathcal{I}| \leq t_1 + t_2$  (resp. with  $|\mathcal{I}| \leq t_1$ );

- 2.  $\mathcal{S}_{G,\mathcal{W},\mathcal{O}}^{(2)}(\boldsymbol{x}_{|\mathcal{I}}) \stackrel{\mathrm{id}}{=} G_{\mathcal{W}\cup\mathcal{O}}(\boldsymbol{x}).$

A v-refresh gadget is simply said to be NI (resp. SNI) if it is (n-1)-NI (resp. (n-1)-SNI).

If a gadget achieves NI-security, then a probe of an internal wire or an output wire can be simulated using one probe on each of the input sharings of the gadget. If it achieves the stronger SNI-security notion then only probes of internal wires are propagated to inputs (and it thus guarantees independence between the inputs and outputs even with access to the internal wires).

For a v-refresh gadget, the PINI notion is defined as follows:

**Definition 7** (PINI). Let  $\mathbf{v} \in (\mathbb{K}^*)^n$  and let G be a  $\mathbf{v}$ -refresh gadget with s wires. G is said t-Probe Isolating Non-Interferent (t-PINI), if for every  $\mathbf{x}$  and every set of internal wires  $\mathcal{W} \subseteq [s]$  with  $|\mathcal{W}| \le t_1$  and every set of output wires  $\mathcal{O} \subseteq [s]$  with  $|\mathcal{O}| \le t_2$  and  $t_1 + t_2 \le t$ , there exists a (two-stage) simulator  $\mathcal{S}_{G,\mathcal{W},\mathcal{O}} = (\mathcal{S}_{G,\mathcal{W},\mathcal{O}}^{(1)}, \mathcal{S}_{G,\mathcal{W},\mathcal{O}}^{(2)})$  such that

- 1.  $\mathcal{S}_{G,\mathcal{W},\mathcal{O}}^{(1)}(\perp) = \mathcal{I}$  where  $\mathcal{I} \subseteq [n]$ , with  $|\mathcal{I}| \leq t_1$ ;

- 2.  $\mathcal{S}_{G.W.\mathcal{O}}^{(2)}(\boldsymbol{x}_{|\mathcal{I}\cup\mathcal{J}}) \stackrel{\mathrm{id}}{=} G_{W\cup\mathcal{O}}(\boldsymbol{x});$

where  $\mathcal{J} \subseteq [n]$  is the set of indices of output shares in  $\mathcal{O}$ . A  $\boldsymbol{v}$ -refresh gadget is simply said to be PINI if it is (n-1)-PINI.

**Comparison of the composition approaches.** We discuss hereafter the composition approaches related to the (S)NI notion, the PINI notion and our new IOS notion.

(S)NI composition approach. The NI and SNI notions were proposed in [BBD<sup>+</sup>16] as composition notions for probing-secure gadgets. The authors show how to compose t-NI and t-SNI gadgets to achieve t-probing security, which was further generalized in [BGR18]. Theses results can actually be extended to region probing security. Let us consider the standard circuit compiler as defined in Section 2. If the underlying refresh gadget is SNI and the underlying addition and multiplication gadgets are NI, then it can be checked that the compiled circuit can tolerate up to t/2 probes per gadget. In other words, from an SNI refresh gadget, one simply needs NI operation gadgets to obtain a region probing-secure composition.

PINI composition approach. The PINI notion was introduced to allow trivial composition of probing-secure gadgets [CS20]. Specifically composing any number of PINI gadgets in any way results in a circuit achieving PINI security which further implies probing security. Another advantage of the PINI notion is that it is satisfied by any sharewise gadget (i.e. a gadget which simply applies an operation sharewisely) without requiring any refreshing or randomness. Although the PINI notion enables simpler composition, it is limited to probing security (or PINI security) and cannot be extended to region probing security. To illustrate this impossibility, let us consider the following simple example. Suppose that some circuit compiler applies a single-input sharewise gadget G (for instance squaring on  $\mathbb{F}_{256}$ ) successively many times to an input n-sharing x. After N gadgets each leaking t probes, all the shares can be recovered whenever N > n/t.

IOS composition approach. Our composition approach consists in interleaving an IOS refresh gadget between any pair of successive operation gadgets of the compiled circuit (as in the definition of the standard circuit compiler). Doing so, we can lower the requirement on the operation gadgets: they simply needs to achieve the weaker notion of probing security (see Theorem 1 above).

Comparison. We compare the three composition approaches for the standard circuit compiler as introduced in Section 2. This compiler basically replaces each gate by the corresponding operation gadget and it interleaves a refresh gadget in each connection between two operation gadgets. Assuming that the refresh gadget satisfies a given notion in  $\{SNI, PINI, IOS\}$ , we look at (i) what is the security notion required for the operation gadgets? (ii) what is the obtained security notion for the composed circuit?

#### • SNI:

- (i) The **NI** notion is sufficient for the operation gadgets.

- (ii) The composition of NI operation gadgets and SNI refresh gadgets implies the region probing security of the composed circuit.

#### • PINI:

- (i) The **PINI** notion is sufficient for the operation gadgets.

- (ii) The composition of PINI gadgets implies the **probing security** of the composed circuit. Let us stress that with PINI operation gadgets, PINI refresh gadgets are actually useless.

#### • IOS:

- (i) The **probing security** is sufficient for the operation gadgets.

- (ii) The composition of probing-secure operation gadgets and IOS refresh gadgets implies the **region probing security** of the composed circuit.

Our composition approach, hence achieves the stronger notion of region probing security from the weaker notion of probing security for operation gadgets based on the IOS security of the refresh gadget.

Relations between (S)NI, PINI and IOS. We now discuss the relations between the three notions, for a single-input single-output gadget, typically a refresh gadget. For such gadgets, SNI security readily implies PINI security. Since the SNI and PINI definitions do not require uniformity of the gadget, these notion do not imply IOS-security. However, one can show that a refresh gadget which is PINI and uniform (or SNI and uniform) achieves our IOS notion. Indeed, given a set of wires  $\mathcal{W} \subseteq [s]$  with  $\mathcal{W} = \mathcal{W}' \cup \mathcal{O}$  with  $\mathcal{W}'$  the set of internal wires and  $\mathcal{O}$  the set of output wires, the IOS-simulator  $\mathcal{S}^{(1)}_{G,\mathcal{W}}$  simply runs the PINI-simulator  $\mathcal{S}^{(2)}_{G,\mathcal{W}',\mathcal{O}}(\bot)$  to get a set  $\mathcal{I}'$  and sets  $\mathcal{I} = \mathcal{I}' \cup \mathcal{O}$  and  $\mathcal{J} = \emptyset$ . The IOS-simulator  $\mathcal{S}^{(2)}_{G,\mathcal{W}',\mathcal{O}}(\bot)$  on input  $\mathbf{x}_{|\mathcal{I}'\cup\mathcal{O}}$  until it obtains a simulation matching  $\mathbf{y}_{|\mathcal{J}}$  (which eventually occurs by uniformity).

Any uniform SNI or PINI refresh gadget can then be used as an IOS refresh gadget in our composition framework. However, simpler gadget designs might achieve the IOS notion without achieving the SNI or PINI notions. We give an example of such a refresh gadget in the next section.

# 4 An Input-Output Separative Refresh Gadget

Battistello, Coron, Prouff and Zeitoun propose in [BCPZ16a] the so-called (template) horizontal side-channel attacks against the ISW [ISW03] and the Rivain-Prouff [RP10] secure multiplication schemes. These attacks exploit the fact that, for those schemes, the leaking information on each share increases with the number of shares in the presence of a constant leakage rate. Battistello  $et\ al.$  describe a variant of the ISW multiplication with probing-security that is heuristically secure against this kind of attacks. In the full version of their paper [BCPZ16b], they further propose a new refreshing gadget with complexity  $O(n\log n)$ . In this section, we simplify and extend their gadget for any v-linear sharing and we prove that it achieves the IOS security notion.

#### 4.1 Refresh Gadget Description

The modified refresh gadget RefreshGadget is described in Algorithm 1. It is defined recursively: for n=2, given a  $\boldsymbol{v}$ -linear sharing  $\boldsymbol{x}=(x_1,x_2)$  it outputs  $\boldsymbol{y}=(y_1,y_2)=(x_1+r,x_2-r\cdot v_1\cdot v_2^{-1})$  such that  $\langle \boldsymbol{y},\boldsymbol{v}\rangle=\langle \boldsymbol{x},\boldsymbol{v}\rangle$  and for  $n\geq 4$  a power of 2, the RefreshGadget gadget is applied recursively on the two halves of the share (Steps 4-5) and a post-processing layer is applied to the whole sharing (Steps 6-9). Note that the

original refresh gadget proposed in [BCPZ16a] makes use of an additional and similar pre-processing layer before the two recursive calls to the RefreshGadget gadget, but this layer is not necessary to achieve the IOS property. It results that our variant is twice more efficient in terms of computation and randomness generation.

#### Algorithm 1 RefreshGadget

```

Require: \boldsymbol{x} = (x_1, \dots, x_n), \, \boldsymbol{v} = (v_1, \dots, v_n),

Ensure: \boldsymbol{y} = (y_1, \dots, y_n) such that \langle \boldsymbol{y}, \boldsymbol{v} \rangle = \langle \boldsymbol{x}, \boldsymbol{v} \rangle

1: if n = 2 then

2: r \overset{R}{\leftarrow} \mathbb{F}

3: return (x_1 + r, x_2 - r \cdot v_1 \cdot v_2^{-1})

4: (s_1, \dots, s_{n/2}) \leftarrow \text{RefreshGadget}(a_1, \dots, a_{n/2}; v_1, \dots, v_{n/2}) \triangleright Recursive call

5: (s_{n/2+1}, \dots, s_n) \leftarrow \text{RefreshGadget}(a_{n/2+1}, \dots, a_n; v_{n/2+1}, \dots, v_n) \triangleright Recursive call

6: for i = 1, \dots, n/2 do

7: r_i \overset{R}{\leftarrow} \mathbb{F}

8: y_i \leftarrow s_i + r_i

9: y_{i+n/2} \leftarrow s_{i+n/2} - r_i \cdot v_i \cdot v_{i+n/2}^{-1}

```

Let us denote R(n), A(n) and M(n) the randomness complexity, the number of additions and the number of scalar multiplications of the RefreshGadget algorithm for length-n linear sharing. We have R(2)=1, A(2)=2 and M(2)=1 and R(2n)=2R(n)+n, A(2n)=2A(n)+2n and M(2n)=2M(n)+n for all  $n\geq 2$ . By induction, we thus have for any  $n\geq 2$ , a power of 2, we obtain

$$R(n) = M(n) = n\log(n)/2 \text{ and } A(n) = n\log(n).$$

(2)

#### 4.2 Proof of Input-Output Separation

**Theorem 2.** The refresh gadget from Algorithm 1 is input-output separative.

*Proof.* Throughout the proof, we denote by  $L = \left[\frac{n}{2}\right]$  and  $H = [n] \setminus L$ .

Uniformity. Let  $\mathbf{v} \in (\mathbb{K}^*)^n$ . We show that the  $\mathbf{v}$ -refresh gadget RefreshGadget is uniform, namely that if for every  $\mathbf{x} \in \mathbb{K}^n$ , the output RefreshGadget( $\mathbf{x}$ ) is a uniform  $\mathbf{v}$ -linear sharing of  $\langle \mathbf{v}, \mathbf{x} \rangle$ . The proof is by induction on n.

For n=2, given  $\boldsymbol{x}=(x_1,x_2)\in\mathbb{K}^2$ , the gadget outputs  $\boldsymbol{y}=(y_1,y_2)$  defined as  $(x_1+r,x_2-r\cdot v_1\cdot v_2^{-1})$  where r is picked uniformly at random in  $\mathbb{K}$  and one can see readily that  $\boldsymbol{b}$  is a uniformly distributed  $\boldsymbol{v}$ -linear sharing of  $\langle \boldsymbol{v},\boldsymbol{x}\rangle$ .

For  $n \geq 4$ , given  $\boldsymbol{x} = (x_1, x_2, \dots, x_n) \in \mathbb{K}^2$ , the gadget first computes  $(s_1, \dots, s_{n/2})$  and  $(s_{n/2+1}, \dots, s_n)$  as outputs of RefreshGadget $(x_1, \dots, x_{n/2})$  and RefreshGadget $(x_{n/2+1}, \dots, x_n)$ . By the induction hypothesis,  $\boldsymbol{s}_{|L} = (s_1, \dots, s_{n/2})$  and  $\boldsymbol{s}_{|H} = (s_{n/2+1}, \dots, s_n)$  are uniform and independent  $\boldsymbol{v}_{|L} = (v_1, \dots, v_{n/2})$ -linear sharing and  $\boldsymbol{v}_{|H} = (v_{n/2+1}, \dots, v_n)$ -linear sharing of  $\langle \boldsymbol{v}_{|L}, \boldsymbol{x}_{|L} \rangle$  and  $\langle \boldsymbol{v}_{|H}, \boldsymbol{x}_{|H} \rangle$  (respectively) where  $\boldsymbol{x}_{|L} = (x_1, \dots, x_{n/2})$  and  $\boldsymbol{x}_{|H} = (x_{n/2+1}, \dots, x_n)$ . The gadget RefreshGadget then picks uniformly at random  $r_i$  in  $\mathbb{K}$  for  $i \in L$  and sets  $y_i = s_i + r_i$  and  $y_{i+n/2} = s_{i+n/2} - r_i \cdot v_i \cdot v_{i+n/2}^{-1}$  for  $i \in L$ . Denoting  $r_i' = s_i + r_i(=y_i)$  for  $i \in L$  the vector  $(r_1', \dots, r_{n/2}')$  is uniformly distributed in  $\mathbb{K}^{n/2}$  and independent from  $\boldsymbol{c}$  and we have  $y_{i+n/2} = s_{i+n/2} - (r_i' - s_i) \cdot v_i \cdot v_{i+n/2}^{-1}$  for  $i \in L$  where  $\boldsymbol{s}_{|L}$  and  $\boldsymbol{s}_{|H}$  are uniform and independent  $\boldsymbol{v}_{|L}$ -linear sharing and  $\boldsymbol{v}_{|H}$ -linear sharing of  $\langle \boldsymbol{v}_{|L}, \boldsymbol{x}_{|L} \rangle$  and  $\langle \boldsymbol{v}_{|H}, \boldsymbol{x}_{|H} \rangle$ . The vector  $\boldsymbol{d}$  is therefore a uniformly distributed  $\boldsymbol{v}$ -linear sharing of  $\langle \boldsymbol{v}_{|L}, \boldsymbol{x}_{|L} \rangle$  and  $\langle \boldsymbol{v}_{|H}, \boldsymbol{x}_{|H} \rangle$ . The vector  $\boldsymbol{d}$  is therefore a uniformly distributed  $\boldsymbol{v}$ -linear sharing of  $\langle \boldsymbol{v}_{|L}, \boldsymbol{x}_{|L} \rangle$  and  $\langle \boldsymbol{v}_{|H}, \boldsymbol{x}_{|H} \rangle$ . The vector  $\boldsymbol{d}$  is therefore a uniformly distributed  $\boldsymbol{v}$ -linear sharing of  $\langle \boldsymbol{v}_{|L}, \boldsymbol{x}_{|L} \rangle$

IOS. We now show the IOS property. In the following we shall denote by  $\mathbf{w} = G_{\mathcal{W}}(\mathbf{x}, \mathbf{y})$  the wire distribution for  $\mathcal{W}$  induced by  $(\mathbf{x}, \mathbf{y})$ . Without loss of generality, we assume that

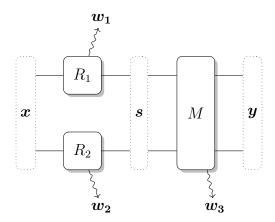

**Figure 2:** IOS refresh gadget with pobes  $(w_1, w_2, w_3)$ .

if the attacker probes a product of a random value  $r_i$  by some publicly known constant (such as the value  $r_i \cdot v_i \cdot v_{i+n/2}^{-1}$  which appear in Step 9), then it can be replaced by an attacker which probes directly the random value  $r_i$ . We show how to achieve a perfect simulation of  $\boldsymbol{w}$  from  $\boldsymbol{x}_{|I|}$  and  $\boldsymbol{y}_{|J|}$  for two sets I and J such that  $|I| \leq |\mathcal{W}|$  and  $|J| \leq |\mathcal{W}|$ . The case  $|\mathcal{W}| \geq n$  is straightforward: we let I = J = [n] and we can simulate  $\boldsymbol{w}$  (and more generally all the wires of G) directly from the full sharings  $(\boldsymbol{x}, \boldsymbol{y})$  and by picking a random tape uniformly for the set  $\{\boldsymbol{\rho} \in \mathbb{K}^q : G_{\mathcal{W}}^{\boldsymbol{\rho}}(\boldsymbol{x}) = \boldsymbol{y}\}$ . We therefore consider  $|\mathcal{W}| < n$  in the following. The proof also works by induction on n.

For n=2, we have  $|\mathcal{W}| \leq 1$ . The case  $|\mathcal{W}| = 0$  is straightforward. For  $|\mathcal{W}| = 1$ , the tuple  $\boldsymbol{w}$  consists in a single variable among  $x_1$ ,  $x_2$ ,  $y_1$ ,  $y_2$ , and r, the output of the single random gate. If the variable is either  $x_1$ ,  $y_1$  or r, we let  $I=J=\{1\}$ , otherwise we let  $I=J=\{2\}$ . The simulation is straightforward for any  $x_i$  or  $y_i$ . For r, we simply let  $r=y_1-x_1$ .

For  $n \geq 2$ , we denote  $R_1$  the gadget corresponding to the first recursive call to RefreshGadget (Step 4),  $R_2$  the gadget corresponding to the second recursive call to RefreshGadget (Step 5) and M the gadget corresponding to the post-processing layer (Steps 6-9). We denote by  $\mathcal{W}_1$ ,  $\mathcal{W}_2$ , and  $\mathcal{W}_3$ , the subset of  $\mathcal{W}$  corresponding to wire indexes from  $R_1$ ,  $R_2$ , and M respectively, so that  $\mathcal{W} = \mathcal{W}_1 \cup \mathcal{W}_2 \cup \mathcal{W}_3$ . Without loss of generality, all the outputs of  $R_1$  and  $R_2$ , which are also inputs of M, are included to  $\mathcal{W}_1$  and  $\mathcal{W}_2$ , but not to  $\mathcal{W}_3$ . We further denote  $t_1 = |\mathcal{W}_1|$ ,  $t_2 = |\mathcal{W}_2|$ , and  $t_3 = |\mathcal{W}_3|$ , so that

$$t_1 + t_2 + t_3 = |\mathcal{W}| < n ,$$

as well as  $\mathbf{w}_1 = G_{\mathcal{W}_1}(\mathbf{x}, \mathbf{y}), \mathbf{w}_2 = G_{\mathcal{W}_2}(\mathbf{x}, \mathbf{y}), \text{ and } \mathbf{w}_3 = G_{\mathcal{W}_3}(\mathbf{x}, \mathbf{y}), \text{ so that}$

$$(\boldsymbol{w}_1, \boldsymbol{w}_2, \boldsymbol{w}_3) = \boldsymbol{w}$$

.

Let  $\mathbf{s} = (s_1, \ldots, s_n)$  denote the linear sharing in output of the block  $(R_1 \parallel R_2)$ , and  $\mathbf{s}_{|L} = (s_1, \ldots, s_{\frac{n}{2}})$  and  $\mathbf{s}_{|H} = (s_{\frac{n}{2}+1}, \ldots, s_n)$  be the respective output of  $R_1$  and  $R_2$ . By definition of the layer M, we have  $\langle \mathbf{v}_{|L}, \mathbf{s}_{|L} \rangle + \langle \mathbf{v}_{|H}, \mathbf{s}_{|H} \rangle = \langle \mathbf{v}_{|L}, \mathbf{y}_{|L} \rangle + \langle \mathbf{v}_{|H}, \mathbf{y}_{|H} \rangle$ . On the other hand, the gadgets  $R_1$  and  $R_2$  are uniform, which implies that the tuples  $\mathbf{s}_{|L}$  and  $\mathbf{s}_{|H}$  are uniformly distributed among the tuples of  $\mathbb{K}^{\frac{n}{2}}$  satisfying

$$\langle \boldsymbol{v}_{|L}, \boldsymbol{s}_{|L} \rangle = \langle \boldsymbol{v}_{|L}, \boldsymbol{x}_{|L} \rangle,$$

(3)

$$\langle \boldsymbol{v}_{|H}, \boldsymbol{s}_{|H} \rangle = \langle \boldsymbol{v}_{|H}, \boldsymbol{x}_{|H} \rangle ) ,$$

(4)

$$\langle \boldsymbol{v}_{|L}, \boldsymbol{s}_{|L} \rangle + \langle \boldsymbol{v}_{|H}, \boldsymbol{s}_{|H} \rangle = \langle \boldsymbol{v}_{|L}, \boldsymbol{y}_{|L} \rangle + \langle \boldsymbol{v}_{|H}, \boldsymbol{y}_{|H} \rangle , \qquad (5)$$

By induction  $R_1$  and  $R_2$  are IOS, which implies that we can perfectly simulate  $(\boldsymbol{w}_1, \boldsymbol{w}_2)$  from  $\boldsymbol{x}_{|I_1}, \boldsymbol{x}_{|I_2}, \boldsymbol{s}_{|J_1}$ , and  $\boldsymbol{s}_{|J_2}$  for some sets  $I_1, J_1 \subseteq L$ ,  $I_2, J_2 \subseteq H$ , such that  $|I_1|, |J_1| \leq t_1$ , and  $|I_2|, |J_2| \leq t_2$ . Without loss of generality, if  $t_1 \geq \frac{n}{2}$ , we let  $I_1 = J_1 = L$ , and if  $t_2 \geq \frac{n}{2}$ , we let  $I_2 = J_2 = H$ .

The set I is simply constructed as  $I = I_1 \cup I_2$ . We show hereafter how to achieve a perfect simulation of  $(s_{|J_1}, s_{|J_2}, w_3)$  from  $x_{|I}$  and  $y_{|J}$  for some set J such that  $|J| \leq |\mathcal{W}|$ . As depicted in Figure 3, we will hence get a perfect simulation of  $(w_1, w_2, w_3) = w$  from  $x_{|I|}$  and  $y_{|J|}$  which shall complete the proof.

**Figure 3:** Overview of the simulation process.

We now show how to achieve a perfect simulation of  $(s_{|J_1}, s_{|J_2}, w_3)$  from  $x_{|I}$  and  $y_{|J}$  for some set J such that  $|J| \leq |\mathcal{W}|$ . Let  $\mathcal{V}_i$  denote the set of variables  $\{s_i, r_i, y_i, s_{i+\frac{n}{2}}, y_{i+\frac{n}{2}}\}$ . All the variables in  $(s_{|J_1}, s_{|J_2}, w_3)$  are included in  $\bigcup_{i \in L} \mathcal{V}_i$ , where

- $s_{|J_1}$  contains some of the  $(s_i)_{i\in L}$ ;

- $s_{|J_2|}$  contains some of the  $(s_{i+\frac{n}{2}})_{i\in L}$ ;

- $w_3$  contains some of the  $(r_i)_{i\in L}$ ,  $(y_i)_{i\in L}$ , and  $(y_{i+\frac{n}{2}})_{i\in L}$ .

We construct J as follows. For every  $i \in L$ :

- if two or more variables from  $V_i$  appear in  $(s_{|J_1}, s_{|J_2}, w_3)$ , we include i and  $i + \frac{n}{2}$  to J;

- if one single variable from  $V_i$  appears in  $(s_{|J_1}, s_{|J_2}, w_3)$ ,

- if the variable is  $s_i$ ,  $r_i$ , or  $y_i$ , we include i to J;

- if the variable is  $s_{i+\frac{n}{2}}$ , or  $y_{i+\frac{n}{2}}$ , we include  $i+\frac{n}{2}$  to J;

- if no variables from  $V_i$  appear in  $(\mathbf{s}_{|J_1}, \mathbf{s}_{|J_2}, \mathbf{w}_3)$ , we do not include i nor  $i + \frac{n}{2}$  to J.

Clearly the number of indices added to J is at most the number of variables in  $(s_{|J_1}, s_{|J_2}, w_3)$ , that is

$$|J| \le |J_1| + |J_2| + t_3 \le t_1 + t_2 + t_3 = |\mathcal{W}|$$

.

We now explain how to simulate  $(s_{|J_1}, s_{|J_2}, w_3)$  from  $x_{|I}$  and  $y_{|J}$  while satisfying the constraints (3), (4) and (5).

Let us first assume that we have  $t_1 < \frac{n}{2}$  and  $t_2 < \frac{n}{2}$ . This implies that not all the  $(s_i)_{i \in L}$  (resp. the  $(s_{i+\frac{n}{2}})_{i \in L}$ ) have to be simulated, which releases the constraints (3) and (4). By construction of J, the  $(y_i)_{i \in L}$  and  $(y_{i+\frac{n}{2}})_{i \in L}$  that appear in  $(s_{|J_1}, s_{|J_2}, w_3)$  are also included in  $y_{|J|}$  and can thus be straightly and perfectly simulated. Then, for every  $i \in L$ :

• if  $\{i, i + \frac{n}{2}\} \subseteq J$ , we can perfectly simulate  $s_i, r_i, s_{i+\frac{n}{2}}$  from  $y_i$  and  $y_{i+\frac{n}{2}}$  as

$$r_i \leftarrow \mathbb{K}$$

$$s_i \leftarrow y_i + r_i$$

$$s_{i+\frac{n}{2}} \leftarrow y_{i+\frac{n}{2}} - r_i \cdot v_i \cdot v_{i+n/2}^{-1}$$

• if  $i \in J$  and  $i + \frac{n}{2} \notin J$ , we can perfectly simulate  $s_i$  and  $r_i$  from  $y_i$  as

$$r_i \leftarrow \mathbb{K}$$

$$s_i \leftarrow y_i + r_i$$

• if  $i \notin J$  and  $i + \frac{n}{2} \in J$ , we can perfectly simulate  $s_{i+\frac{n}{2}}$  from  $y_{i+\frac{n}{2}}$  as

$$r_i \leftarrow \mathbb{K}$$

$$s_{i+\frac{n}{2}} \leftarrow y_{i+\frac{n}{2}} - r_i \cdot v_i \cdot v_{i+n/2}^{-1}$$

This way we have completed a full simulation of all the variables appearing in  $(s_{|J_1}, s_{|J_2}, w_3)$  while satisfying the constraint (5).

Let us now relax the assumption on  $t_1$  and  $t_2$ . Since  $t_1 + t_2 < n$  we have  $t_1 < \frac{n}{2}$  or  $t_2 < \frac{n}{2}$ . Without loss of generality, we assume  $t_2 < \frac{n}{2}$  (the case  $t_1 < \frac{n}{2}$  would be handled similarly). Therefore we might have  $t_1 \ge \frac{n}{2}$  implying  $I_1 = J_1 = L$ ,  $L \subseteq I$  and  $L \subseteq J$ . In that case, we must simulate all the  $(s_i)_{i \in L}$  while satisfying the constraint (3). The simulation works as above, but we keep one index  $i^* \in L$  for which  $i^* + \frac{n}{2} \notin J$  for the end of the simulation (such an index exists otherwise we would have  $|J| = n > |\mathcal{W}|$ ). For this index  $i^*$ , we can perfectly simulate  $s_{i^*}$  and  $r_{i^*}$  from  $\mathbf{x}_{|I_1} = \mathbf{x}_{|L}$ ,  $(s_i)_{i \in L \setminus \{i^*\}}$  and  $y_{i^*}$  as

$$s_{i^*} \leftarrow \langle \boldsymbol{v}_{|L}, \boldsymbol{x}_{|L} \rangle - \sum_{i \in L \setminus \{i^*\}} s_i \cdot v_i$$

$$r_{i^*} \leftarrow y_{i^*} - s_{i^*}$$

We thus achieve a perfect simulation of  $(s_{|J_1}, s_{|J_2}, w_3)$  from  $x_{|I}$  and  $y_{|J}$  while satisfying the constraints (3), (4) and (5), which concludes the proof.

# 5 Revisiting the GJR Masking Scheme

In this section, we revisit the quasilinear-complexity Goudarzi-Joux-Rivain (GJR) masking scheme [GJR18]. We first describe a variant of this scheme making use of the IOS refresh gadget described above and which is more general than the original scheme in the sense that it works on any base field  $\mathbb K$  equipped with an Fast Fourier Transform (FFT) for multiple-point polynomial evaluation. We then show that the use of our refresh allows to patch a flaw in the security proof of the original scheme. We shall refer to the improved GJR scheme as the GJR<sup>+</sup> scheme hereafter.

#### 5.1 The GJR<sup>+</sup> Scheme

As in the original scheme, the GJR<sup>+</sup> scheme is based on so called  $\omega$ -encodings which are  $v_{\omega}$ -linear sharings with

$$\mathbf{v}_{\omega} = (1, \omega, \dots, \omega^{n-1}) \ . \tag{6}$$

For such a vector, a sharing  $\boldsymbol{x}=(x_1,x_2,\ldots,x_n)$  of a plain value  $x\in\mathbb{K}$  can be seen as the coefficients of a polynomials  $P_{\boldsymbol{x}}=\sum_{i=1}^n x_i\cdot\alpha^{i-1}\in\mathbb{K}[\alpha]$  such that  $P_{\boldsymbol{x}}(\omega)=x$ . The quasilinear complexity can then be achieved by using efficient FFT-based multiplication for the multiplication gadget. Note that such encoding is close to but different from *Shamir's secret sharing* [Sha79]. In the latter the shares are defined as evaluations of a polynomial in fixed points and for which the plain value is the degree-0 coefficient.

We assume the existence of a Fast Fourier Transform (FFT) algorithm that, given any polynomial  $P \in \mathbb{K}[\alpha]$  of degree < 2n, maps the coefficients of P to the evaluations of P

over 2n points of  $\mathbb{K}$ , with a complexity of  $\widetilde{O}(n)$  operations. That is:

$$\mathsf{FFT}_{\alpha} : (x_1, x_2, \dots, x_{2n}) \mapsto (u_1, u_2, \dots, u_{2n}) \quad \text{with} \quad u_j = \sum_{i=1}^{2n} x_i \cdot \alpha_j^{i-1}$$

for every  $j \in [2n]$ , for some  $\boldsymbol{\alpha} = (\alpha_1, \alpha_2, \dots, \alpha_{2n}) \in \mathbb{K}^{2n}$ . We further assume that this FFT algorithm can be written as an arithmetic circuit on  $\mathbb{K}$  solely composed of additions, subtractions and multiplication by constants in  $\mathbb{K}$ , and that it features an inverse FFT algorithm with the same properties (in terms of type and number of operations).

The GJR<sup>+</sup> scheme is a standard circuit compiler for  $(\mathcal{V}, \mathcal{G}^{\oplus}, \mathcal{G}^{\otimes}, \mathcal{G}^{\mathsf{R}})$  (see definition in Section 2), with  $\mathcal{V} = \{v_{\omega}^{(n)}\}_{n \in \mathbb{N}}$  where  $v_{\omega}^{(n)} \in \mathbb{K}^n$  is the vector defined in (6). As in the original scheme, we assume in the following that the order n is a power of two. The scheme could be easily extended to deal with non-power of two at the cost of a small constant efficiency factor.

We now give the description of the associated  $v_{\omega}^{(n)}$ -gadgets. For the sake of clarity we shall omit the superscript and simply note  $v_{\omega}$  in what follows.

**Refresh Gadget.** We use the refresh gadget of Section 4 (see Algorithm 1) for  $v_{\omega}$ -sharings *i.e.* with encoding vector v assigned to  $v_{\omega}$ . This refresh gadget is applied in output of each operation gadget (in accordance to the definition of the standard circuit compiler). We recall that this gadget achieves the uniformity and IOS properties defined in Subsection 3.1.

**Addition Gadget.** Given two  $\boldsymbol{v}_{\omega}$ -sharings  $\boldsymbol{x}=(x_1,\ldots,x_n)$  and  $\boldsymbol{y}=(y_1,\ldots,y_n)$ , the addition gadget outputs

$$\boldsymbol{x} + \boldsymbol{y} = (x_1 + y_1, \dots, x_n + y_n) .$$

This is done via n addition gates processing each share separately. Hence this addition gadget achieves (n-1)-probing security.

**Subtraction Gadget.** Given two  $v_{\omega}$ -sharings  $\boldsymbol{x} = (x_1, \dots, x_n)$  and  $\boldsymbol{y} = (y_1, \dots, y_n)$ , the subtraction gadget outputs

$$\boldsymbol{x} - \boldsymbol{y} = (x_1 - y_1, \dots, x_n - y_n) .$$

This is done via n subtraction gates processing each share separately. Hence this subtraction gadget achieves (n-1)-probing security.

**Multiplication Gadget.** Let  $v_{\omega}' \in \mathbb{K}^{2n}$  be the vector defined as

$$v_{\omega}' = \mathsf{FFT}_{\alpha}^{-1}(1, \omega, \omega^2, \dots, \omega^{2n-1})$$

.

Let Compress be the  $\mathbb{K} \times \mathbb{K}^{2n} \to \mathbb{K}^n$  mapping defined as

Compress

$$(\omega; t_1, t_2, \dots, t_{2n}) = (t_1 + \omega^n \cdot t_{n+1}, t_2 + \omega^n \cdot t_{n+2}, \dots, t_n + \omega^n \cdot t_{2n})$$

Let **0** denotes the *n*-dimensional all-0 vector and  $\parallel$  denote the concatenation operator. Given two  $v_{\omega}$ -sharings x and y, the multiplication gadget proceeds as

- 1.  $r \leftarrow \mathsf{FFT}_{\alpha}(x \parallel 0)$

- 2.  $s \leftarrow \mathsf{FFT}_{\alpha}(y \parallel 0)$

- 3.  $u \leftarrow r \cdot s$

- 4.  $\boldsymbol{u}' \leftarrow \mathsf{Refresh}(\boldsymbol{v}'_{\omega}; \boldsymbol{u})$

- 5.  $t \leftarrow \mathsf{FFT}_{\alpha}^{-1}(u')$

- 6.  $z \leftarrow \mathsf{Compress}(\omega; t)$

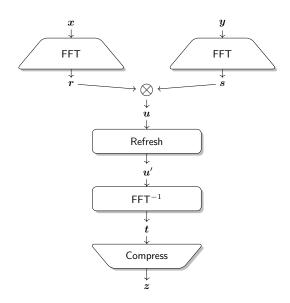

Figure 4: Multiplication gadget.

and outputs z. Note that r, s, u, u', t are (2n)-dimensional vectors. Only the input/output sharings x, y and z are n-dimensional vectors. The procedure is depicted on Figure 4 for illustration.

Remark. This multiplication gadget is similar to the GJR multiplication gadget but we introduce a refreshing in Step 4. This refreshing is done using Algorithm 1 (see Section 4) where the encoding vector  $v'_{\omega}$  and the input sharing are of size 2n.

Correctness. Let x and y be the values encoded by x and y respectively and let  $P_x \in \mathbb{K}[\alpha]$ and  $P_y \in \mathbb{K}[\alpha]$  be the degree-(n-1) polynomials whose coefficients are the coordinates of  $\boldsymbol{x}$  and  $\boldsymbol{y}$ , so that we have  $P_{\boldsymbol{x}}(\omega) = x$  and  $P_{\boldsymbol{y}}(\omega) = y$ .

Let us first assume that Step 4 applies an identity mapping, i.e. u' = u. Then Steps 1–5 perform a classical FFT-based polynomial multiplication. Namely, the coordinates of tare the coefficients of the polynomial  $P_t \in \mathbb{K}[\alpha]$  such that  $P_t(\alpha) = P_x(\alpha) \cdot P_y(\alpha)$ , and in particular  $P_t(\omega) = x \cdot y$ . Then Step 6 outputs a vector z such that  $\langle v_{\omega}, z \rangle = P_t(\omega) = x \cdot y$ , i.e. a  $\mathbf{v}_{\omega}$ -sharing of  $x \cdot y$ . Let  $\mathbf{v}''_{\omega} = (1, \omega, \omega^2, \dots, \omega^{2n-1})$ , then we have

$$P_{\boldsymbol{t}}(\omega) = \langle \boldsymbol{v}''_{\omega}, \boldsymbol{t} \rangle = x \cdot y \quad \Leftrightarrow \quad \langle \boldsymbol{v}'_{\omega}, \mathsf{FFT}_{\boldsymbol{\alpha}}(\boldsymbol{t}) \rangle = x \cdot y \ .$$

By correctness of the FFT-based polynomial multiplication, we hence have that u= $\mathsf{FFT}_{\alpha}(t)$  is a  $v'_{\omega}$ -sharing of  $x \cdot y$ . Let us now consider the actual multiplication gadget with refreshing at Step 4. By correctness of the refresh algorithm, u' is also a  $v'_{\omega}$ -sharing of  $x \cdot y$ , and by the above relation we have that  $\langle v'_{\omega}, u' \rangle = x \cdot y$  implies  $\langle v''_{\omega}, \mathsf{FFT}^{-1}_{\alpha}(u') \rangle = x \cdot y$ , which is  $\langle \mathbf{v}''_{\omega}, \mathbf{t} \rangle = x \cdot y$ . We hence get the correctness of the multiplication gadget.

Scalar Multiplication Gadget. For the particular case of a multiplication by a constant, a dedicated scalar multiplication gadget can be used which is much more efficient than a regular multiplication gadget. Given a  $\mathbf{v}_{\omega}$ -sharing  $\mathbf{x} = (x_1, \dots, x_n)$  and a constant  $\alpha \in \mathbb{K}$ , the scalar multiplication gadget outputs

$$\alpha \cdot \boldsymbol{x} = (\alpha \cdot x_1, \dots, \alpha \cdot x_n)$$

.

This is done via n multiplication gates processing each share separately. Hence this scalar multiplication gadget achieves (n-1)-probing security.

**Square Gadget.** For the particular case of a field  $\mathbb{K}$  of characteristic 2, a square can be computed through a dedicated gadget much more efficiently than with a regular multiplication gadget. Given a  $\mathbf{v}_{\omega}$ -sharing  $\mathbf{x} = (x_1, \dots, x_n)$  of x, the square gadget outputs

$$\mathbf{y} = (y_1, y_2, \dots, y_n)$$

with  $y_i = x_i^2 \cdot \omega^{i-1}$

for every  $i \in [n]$ . We then have  $\langle \boldsymbol{v}_{\omega}, \boldsymbol{y} \rangle = \langle \boldsymbol{v}_{\omega}, \boldsymbol{y} \rangle^2$  by linearity of the squaring on a field of characteristic 2, which implies that  $\boldsymbol{y}$  is indeed a  $\boldsymbol{v}_{\omega}$ -sharing of  $x^2$ . The square gadget involves 2n multiplication gates processing each share separately. Hence this square gadget achieves (n-1)-probing security. More generally, a sharewise gadget can compute any  $q^k$ -th power on a field of characteristic q (*i.e.* compute the k-th Frobenius map).

Note that, extending the standard circuit compiler to include such gadget is straightforward but it would make the formalism heavier so we skip this extension from our presentation.

#### 5.2 Field Extension and FFT Algorithm

In order to instantiate the GJR<sup>+</sup> scheme, it is necessary to consider an implementation of secure multiplication at order n over a finite field  $\mathbb K$  and an element  $\omega$  such that there exists an FFT algorithm which allows quasilinear multiplication of polynomials of degree at most n and coefficients in  $\mathbb K$  and which can be written as an arithmetic circuit on  $\mathbb K$  solely composed of additions, subtractions and multiplication by constants.

A possible approach (which was used in [GJR18]), is to consider finite fields  $\mathbb{K} = \mathbb{F}_q$  that contain a (2n)-th root of unity  $\omega$  (i.e. such that  $2n \mid q-1$ ). However, most of the time, we cannot choose the underlying algebraic structure and we have to consider a specific cryptographic primitive with a given structure and to implement it securely. In order to extend the original scheme to any finite field  $\mathbb{F}_p^m$  for some prime number p (with  $m \geq 1$ ), we can use the general additive FFT proposed by Cantor in [WZ88, Can89]. In this case we can instantiate it at order n over  $\mathbb{F}_p^\ell$  where  $\ell$  is the minimum even value greater than m such that  $p^\ell \geq 2n$ .