# A White-Box Masking Scheme Resisting Computational and Algebraic Attacks

Okan Seker, Thomas Eisenbarth and Maciej Liśkiewicz

University of Lübeck, Germany {okan.seker,thomas.eisenbarth}@uni-luebeck.de liskiewi@tcs.uni-luebeck.de

Abstract. White-box cryptography attempts to protect cryptographic secrets in pure software implementations. Due to their high utility, white-box cryptosystems (WBC) are deployed by the industry even though the security of these constructions is not well defined. A major breakthrough in generic cryptanalysis of WBC was Differential Computation Analysis (DCA), which requires minimal knowledge of the underlying white-box protection and also thwarts many obfuscation methods. To avert DCA, classic masking countermeasures originally intended to protect against highly related side-channel attacks have been proposed for use in WBC. However, due to the controlled environment of WBCs, new algebraic attacks against classic masking schemes have quickly been found. These algebraic DCA attacks break all classic masking countermeasures efficiently, as they are independent of the masking order.

In this work, we propose a novel generic masking scheme that can resist both DCA and algebraic DCA attacks. The proposed scheme extends the seminal work by Ishai et al. which is probing secure and thus resists DCA, to also resist algebraic attacks. To prove the security of our scheme, we demonstrate the connection between two main security notions in white-box cryptography: probing security and prediction security. Resistance of our masking scheme to DCA is proven for an arbitrary order of protection, using the well-known strong non-interference notion by Barthe et al. Our masking scheme also resists algebraic attacks, which we show concretely for first and second-order algebraic protection. Moreover, we present an extensive performance analysis and quantify the overhead of our scheme, for a proof-of-concept protection of an AES implementation.

**Keywords:** White-box Cryptography · Boolean Masking · Non-linear Masking · Probing Security · Prediction Security · Differential Computation Analysis · Algebraic Attacks

# 1 Introduction

Protecting secrets purely in software is a great challenge, especially if a full system compromise is not simply declared out-of-scope of the security model. With fully homomorphic encryption still complex and computationally expensive [MOO<sup>+</sup>14] and secure enclaves being notoriously buggy at this time [VBPS17, MIE17, BMW<sup>+</sup>18], industry may opt for white-box cryptosystems (WBC) or even be required to do so by industry standards like EMVCo [Pay, BBF<sup>+</sup>19]. White-box cryptography promises implementation security of cryptographic services in pure software solutions, mainly by protecting keys and intermediate cipher states through layers of obfuscation. While white-box cryptography is successfully sold by several companies as one ingredient of secure software solutions

Licensed under Creative Commons License CC-BY 4.0.

Received: 2020-10-15 Accepted: 2020-12-15 Published: 2021-02-23

(e.g. [Gem]), analysis of deployed solutions is lacking, as is a sound framework to analyze white-box implementations. The white-box model assumes the cryptographic primitive to run in an untrusted environment where the white-box adversary has complete control over the implementation. The adversary can read and modify every memory access or intermediate state and can interrupt the implementation at will. White-box cryptography was introduced in 2002 by Chow et al. [CEJVO03b, CEJvO03a]. The main idea of their scheme is to represent a cryptographic algorithm as a network of look-up tables and key-dependent tables. In order to protect the key dependent tables, Chow et al. proposed to use *input and output encodings*. Although the method provides security guarantees for individual tables, the combinations of protected tables still leaks information [BGEC05]. In fact, all published academic proposals for WBC [Kar10, BCD06, LN05, XL09] have been practically broken [BGEC05, DMWP10, LRDM+14, WMGP07].

Cryptanalysis of WBCs usually requires a time-consuming reverse engineering step to surpass included obfuscation layers [GPRW19]. To overcome this, computational analysis of white-box cryptosystems has been proposed. Computational analysis is inspired by physical grey box attacks, mainly side-channel attacks (SCA). Computational analysis attacks, like side-channel attacks, perform a statistical analysis of observable intermediate states of a cryptographic implementation, e.g. via a physical side-channel [KJJ99, GST14, GMO01]; if the implementation is not protected against this kind of attack, the side-channel may reveal critical information, usually the secret key material used. At CHES 2016, Bos et al. [BHMT16] proposed Differential Computation Analysis (DCA) and showed that DCA can extract keys from a wide range of different white-box implementations very efficiently, without requiring a detailed reverse engineering of the implementation. Following this work, further generic computational analysis techniques have been proposed for whitebox implementations, such as Zero Difference Enumeration [BBIJ17], Collision Attacks, and Mutual Information Analysis [RW19]. Alpirez Bock et al. [BBMT18] analyzed the ineffectiveness of internal encodings and explained why DCA works so well in the white-box setting. Even fault attacks [BDL97,BECN+06] have been shown to be an effective method for state and key recovery attacks on white-box implementations [BHMT16, BBB<sup>+</sup>19]. Biryukov et al. [BU18] introduced two new types of fault attacks to reveal the structure of a white-box implementation, an important step of overcoming obfuscation in WBC.

To meet the threat of DCA and other computational analysis, masking schemes provide a natural protection mechanism. Masking splits a sensitive variable x into n shares, such that x can be recovered from d+1 ( $n \ge d+1$ ) shares, while no information can be recovered from fewer than d+1 shares [CJRR99b]. It is a popular and effective countermeasure in the SCA literature. Most important examples are Boolean masking introduced by Ishai et al. [ISW03] which has been generalized by Rivain and Prouff [RP10], Threshold Implementations defined by Nikova et al. [NRS09], and polynomial masking as defined in [RP12] based on Shamir's secret sharing [Sha79]. Recently the idea of combined countermeasures to resist both side-channel and fault attacks were introduced in the literature [SMG16, RMB+17, SFRES18].

As an example for this methodology, we can consider the dedicated masked white-box implementation introduced in [LKK18]. However, the implementation was broken in [RW19]. In addition, for secure WBC, other countermeasures such as fault protection and obfuscation layers need to be added [BU18] and additional randomness should be included in the input [BRVW19], as internal randomness generators could be disabled by the white-box adversary. Furthermore, higher order variants of DCA have been shown to be effective when applied to masked white-box implementations due to the adversary's ability to observe shares without noise [BRVW19]. Although the noise-free environment makes the attack easier, techniques like control flow obfuscation, input/output encodings and shuffling [VCMKS12] create artificial noise in white-box environments [BBIJ17, BRVW19], effectively increasing the complexity of higher order DCA significantly. More devastatingly,

a new class of generic algebraic DCA (or in short algebraic attacks) has been proposed recently [BU18,GPRW19]. Algebraic attacks are able to break masked WBC independently of the masking orders if the masking is linear. Thus, all current masking proposals resisting DCA (or in more general sense computational attacks) are vulnerable to algebraic attacks. Only the scheme defined by [BU18] resists first-order algebraic attacks due to its non-linear structure, but as we will show, does not resist computational attacks.

To sum up, although there exist informal ideas on how to create a secure white-box design that can resist both computational and algebraic attacks, formal and generic constructions with a security analysis are missing.

**Our contribution:** In this paper, we provide the first generic and combined masking scheme that resists state-of-the-art white-box attacks: computational and algebraic attacks. Classic masking schemes can be applied to WBC, however none of them can *individually* achieve security against both attacks. To fill this gap, we examine the ISW transformation introduced by Ishai et al. [ISW03] and extend it to the white-box context.

We improve the ISW transformation by adding a multiplicatively shared nonlinear share. This additional nonlinear share provides security against algebraic attacks. The secret sharing of our masking scheme then consists of two components: linear and non-linear shares: Linear shares to resist computational attacks and non-linear shares to increase the degree of the decoding function and therefore to prevent algebraic attacks. We present the structure of generic masking that resists an arbitrary order computational and first or second-order algebraic attacks in Section 3. To analyze the security of our construction in Section 4, we focus on two security notions in cryptography: probing security addresses security against computational attacks, while prediction security addresses security against algebraic attacks. The probing model was introduced by Ishai et al. [ISW03]. Later it was revised by Rivain et al. [RP10] to a new model called SCA security. The model states that every tuple of n or less intermediate variables must be independent of any sensitive variable. It was shown that an  $n^{th}$ -order Boolean masking scheme provides security against  $n^{th}$ -order SCA. The complexity of computational attacks grows with the masking order. However, the notion is not sufficient to secure a complete block cipher, as stated in [CPRR14], thus a new and stronger notion called t-strong non-interference (t-SNI) was defined in [BBD<sup>+</sup>16]. The stronger t-SNI notion enables the composability of small secure gadgets to generate complex secure constructions. As stated in [BRVW19], an  $n^{th}$ -order masking provides security against  $n^{th}$ -order probing attacks and  $n^{th}$ -order computational attacks with additional obfuscation layers.

To cover algebraic attacks, a new security notion called  $Prediction\ Security$  was defined in [BU18]. The prediction security of a circuit C (with an encoding function E), is based on the probability of an adversary  $(\mathcal{A})$  to accurately predict values of any single function (of  $d^{th}$  order) over intermediate values computed in the circuit C (composed with encoding E). The aim of such a prediction is to distinguish two sequences of plaintexts (chosen by the adversary) by analyzing the corresponding software trace. For example, an  $n^{th}$ -order Boolean masking that is inherently protected against computational attacks is vulnerable against first-order algebraic attacks, since the adversary can utilize a linear function (i.e. a first-order function) and combine a subset of intermediate variables to recover the secret value.

In this work, we further show that the probing security and prediction security notions are incomparable. First, we prove that our masking scheme is indeed secure against computational attacks by showing that it is secure in the probing model with the given order using the non-interference notions by Barthe et al. [BBD<sup>+</sup>16]. We give a concrete construction for first and second-order prediction security and prove their security. We extend the security definitions given in [BU18] and give a novel composability proof for the second-order prediction secure constructions. Besides the formal proofs, we verify the

probing security of our masking scheme using the tool MaskVerif  $[BBC^+19]$  for specific orders. Furthermore, we update and use the tool produced by [BU18] to experimentally verify the first-order prediction security of our scheme. The implementation that can be used with MaskVerif and the updated version of the tool produced by [BU18] is available as open source  $^1$ .

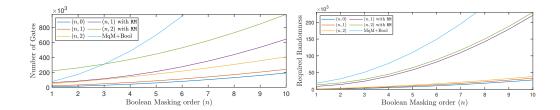

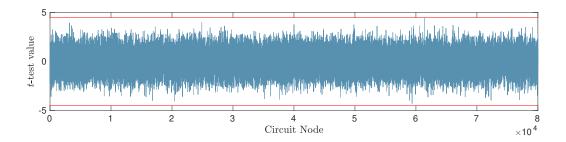

In Section 5 we introduce a proof-of-concept AES implementation to analyze the overhead and experimentally verify the security properties of our scheme using a simple leakage test. The analysis includes the number of needed gates and number of required randomness for different orders of protection. We show that our combined approach outperforms the previous approaches which required to combine two different masking schemes to resist both attacks.

# 2 Preliminaries

In this section, we provide the notation and definitions used throughout this paper. We also identify the challenges that need to be addressed for secure white-box designs.

First, we summarize the notation used throughout the paper. In the following, we use some finite ring  $(\mathbb{K}, \oplus, \otimes)$  with an addition operation  $\oplus$  and a multiplication operation  $\otimes$ . We often omit the multiplication symbol  $\otimes$  and thus write xy instead of  $x \otimes y$ . Although we introduce the notations using  $\mathbb{K}$ , we fix  $\mathbb{K} = \mathrm{GF}(2)$  throughout the paper. A vector space over  $\mathbb{K}$  of dimension  $\ell$  is denoted by  $\mathbb{K}^{\ell}$ . For  $a,b \in \mathbb{Z}$  with a < b, we define  $[a,b] := \{a,a+1,\ldots,b-1,b\}$ . The letters  $x,y,z,\ldots$  represent the sensitive variables. Random variables are represented by the letter r, with an index as  $r_i$  or  $r^i$ . To denote a random selection of a variable r from the field  $\mathbb{K}$ , we use  $r \in_R \mathbb{K}$ .

A sensitive variable x is split into n+1 linear shares  $x_0, \ldots, x_n$  such that  $x = \bigoplus_{i=0}^n x_i$  and a single share (e.g.  $x_0$ ) split into d+1 non-linear shares  $\tilde{x}_0, \ldots, \tilde{x}_d$  such that  $x_0 = \prod_{j=0}^d \tilde{x}_j$ . A vector of elements  $(x_1, \ldots, x_n)$  is denoted by  $\overline{x}$ . For a subset  $I \subseteq [0, n]$  of indices, we denote by  $x_{|I|} = (x_i)_{i \in I}$  the sub-vector of shares indexed by I.

A gadget G for a function  $f: \mathbb{K}^a \to \mathbb{K}^b$  (with regard to a masking order) is an arithmetic circuit with  $a\cdot (n+d+1)$  inputs and  $b\cdot (n+d+1)$  outputs grouped into a vectors of shares  $\overline{x}^{(1)},\ldots,\overline{x}^{(a)}$ , resp. b vectors of shares  $\overline{y}^{(1)},\ldots,\overline{y}^{(b)}$ . The gadget needs to be correct, i.e.  $G(\overline{x}^{(1)},\ldots,\overline{x}^{(a)})=(\overline{y}^{(1)},\ldots,\overline{y}^{(b)})$  iff  $f(x^{(1)},\ldots,x^{(a)})=(y^{(1)},\ldots,y^{(b)})$  for all possible inputs and for all values generated by the random gates. The values assigned to wires that are not output wires are called intermediate variables.

As usual, we model the white-box implementations as Boolean circuits (C) represented by directed acyclic graphs. Each node in a circuit C, with k > 0 inputs, corresponds to a k-ary Boolean function. Nodes with the indegree equal to zero are called inputs of C and nodes with the outdegree equal to zero are called outputs of C.

Let z be an input of  $C: \mathbb{F}_2^N \to \mathbb{F}_2^M$  and  $\overline{\mathsf{x}} = (\mathsf{x}_1, \dots, \mathsf{x}_N)$  be a vector of input nodes in some fixed order. For each node v in C, we say that it computes a Boolean function  $f_v: \mathbb{F}_2^N \to \mathbb{F}_2$  defined as follows:

- for all  $1 \le i \le N$  set  $f_{\times_i}(z) = z_i$ ,

- for all non-input nodes v in C set  $f_v(z) = g_v(f_{c_1}(z), \ldots, f_{c_k}(z))$ , where  $c_1, \ldots, c_k$  are nodes having an outgoing edge to v and  $g_v : \mathbb{F}_2^k \to \mathbb{F}_2$ .

The set of  $f_v$  for all nodes v in C is denoted  $\mathcal{F}(C)$ , the set of  $f_{\mathsf{x}_i}$  for all input nodes  $\mathsf{x}_i$  is denoted  $\mathcal{X}(C)$ , and the set of  $f_v$  for all non-input nodes v in C is denoted  $\mathcal{F}(C \setminus \mathcal{X})$ .

Recall, that any Boolean function  $f: \mathbb{F}_2^n \to \mathbb{F}_2$  has a unique representation of the form  $f(x) = \bigoplus_{b \in \mathbb{F}^n} a_b \ x_1^{b_1} \dots x_n^{b_n}$ , with  $a_b \in \mathbb{F}_2$ . The (algebraic) degree of f, denoted  $\deg(f)$ ,

<sup>1</sup>https://github.com/UzL-ITS/white-box-masking

is the maximum degree of a monomial  $x_1^{b_1} \dots x_n^{b_n}$ , with  $a_b = 1$ . The bias of a Boolean function  $g: \mathbb{F}_2^{\ell} \to \mathbb{F}_2$  is represented by  $\mathcal{E}(\cdot)$  i.e.,  $\mathcal{E}(g) = |1/2 - wt(g)/2^{\ell}|$  and wt(g) is the weight of g, i.e., the number of nonzero entries of its truth table. Bold numbers  $\mathbf{0}$  and  $\mathbf{1}$  are used to denote constant functions.

If  $\mathcal{V} = \{g_1, \dots, g_{|\mathcal{V}|}\}$  is a set of Boolean functions with the same domain  $\mathbb{F}_2^n$  then the d-th order closure of  $\mathcal{V}$  (denoted  $\mathcal{V}^{(d)}$ ) we call the vector space of all functions obtained by composing any function of degree at most d with functions from  $\mathcal{V}$ , i.e.,  $\mathcal{V}^{(d)}$  contains functions of the form  $f \circ (g_1(x), \dots, g_{|\mathcal{V}|}(x))$  for all  $f : \mathbb{F}_2^{|\mathcal{V}|} \to \mathbb{F}_2$ , with  $\deg(f) \leq d$ . For example,  $\mathcal{F}^{(1)}(C)$  is spanned by  $\{1\} \cup \mathcal{F}(C)$  and  $\mathcal{F}^{(2)}(C)$  is spanned by  $\{1\} \cup \{g_ig_j \mid g_i, g_j \in \mathcal{F}(C)\}$ .

Differential Computational Analysis (DCA): The idea of using *side-channel attacks* to recover critical secrets in WBC has been introduced by Bos et al. [BHMT16]. Differential computational analysis utilizes internal states of the software execution (such as memory accesses) to generate software traces. DCA is regarded as one of the most efficient attacks against white-box implementations, since it does not require full knowledge of the white-box design and thus avoids the time-consuming reverse engineering process. The first step of DCA consists of collecting software traces consisting of memory addresses, intermediate values, or values written/read by the implementation. The second step consists of a statistical analysis of the software traces collected during the first step.

As before we use the term *computational attacks* to indicate DCA and higher order variants of DCA. To resist computational attacks, a natural approach is to use the well-known side-channel analysis countermeasure masking [CJRR99b]. Masking is carried out in two steps as defined in the seminal work by Ishai, Sahai, and Wagner in 2003 [ISW03]. First, input data is transformed by representing each input x by n+1 shares in such a way that

$$x = x_0 \oplus \cdots \oplus x_n,$$

where  $x \in \mathbb{F}_2$  and n of the shares are distributed uniformly and independently. Additionally, the circuit is adapted by replacing all AND and XOR gates with gadgets processing the shares of the inputs. Throughout the paper, the data and gate transformation will be defined as ISW transformation.

Masking schemes rely on the availability of good randomness, which is usually provided by secure RNGs, e.g. in the form of a secure and efficient Pseudorandom Generator [IKL<sup>+</sup>13, CGZ19]. Similarly, randomness generation for white-box implementations has been analyzed in the literature. Due to the adversarial ability to control the execution environment in the white-box model, the attacker can simply disable any external randomness sources. Therefore, white-box implementations have to rely on internal randomness sources in combination with additional obfuscation countermeasures [BBIJ17, BU18, BRVW19].

The effectiveness of computational attacks comes from its universality and its ability to avoid reverse-engineering, which can be extremely costly [GPRW19]. By combining masking with an obfuscation layer, the adversary is thus again forced to do a time-consuming reverse engineering step to bypass the obfuscation, while the masking prevents obfuscation-oblivious attacks such as DCA.

Algebraic Attacks: Algebraic attacks have been introduced during the WhibOx contest of CHES2017 [Con]. Although the majority of the implementations in the contest were broken in less than one day, even the strongest design (by means of the surviving time: 28 days) was broken by algebraic analysis [BU18, GPRW19]. Algebraic attacks try to find a set of circuit nodes whose  $d^{th}$ -order of combination equals to a predictable vector. Observe that if an implementation is protected by a linear masking, there exists a set of circuit nodes (corresponding to the secret shares) such that a linear combination (i.e. the

first-order combination) is always equal to a predictable secret value. This means that linear masking is inherently vulnerable to first-order algebraic attacks *independently of the masking order* [BU18, GPRW19]. Like computational attacks, algebraic attacks do not require complex reverse engineering and are thus a generic threat that any white-box implementation needs to address.

Another challenge for secure white-box implementation is the adversaries' ability to collect noise-free measurements. The security of masking schemes against side-channel attacks or computational attacks requires noisy observations [CJRR99a]. To deal with this problem, artificial noise sources such as control flow obfuscation [BBIJ17], shuffling [BRVW19], and input and output encodings [BBMT18] have been analyzed in the literature. The artificial noise introduced by these methods increases the complexity of computational attacks dramatically. It has been shown in [BRVW19] that the complexity of attacks increases with the order of the masking and the order of the obfuscation layers. Therefore, the probing model is a valid approach to analyze the security of masking schemes of white-box implementations against computational attacks. Due to the artificial noise sources, it becomes infeasible for an attacker to combine the required number of shares to recover the sensitive information. Throughout the paper we assume a reliable randomness source is provided as part of the implementation, in other words, randomness can be provided via pseudorandom values derived from the input and protected by obfuscation layers, as done in [BBIJ17, BU18, RW19]. Therefore, the attacks on randomness sources and the adversaries' ability to disable randomness are out-of-scope in this work. For a full white-box implementation, other techniques (fault protection, randomness generation, obscurity layers) need to be added [BU18, BRVW19] in addition to a secure masking scheme, which we introduce throughout this work.

In the next section, we introduce our masking scheme, which resists both computational and algebraic attacks by using an adapted version of the ISW transformation.

# 3 Secure Masking Construction

The proposed masking scheme is based on two ideas: an ISW-like masking to increase the number of shares required to eliminate computation attacks and using a multiplicative sharing to increase the degree of the decoding function. We call the first part linear sharing of order n and the second part non-linear sharing of degree d. The resulting construction is named (n,d)-masking. We start with the data transformation and define our masking function as:

Encode

$$(x, \tilde{x}_0, \dots, \tilde{x}_d, x_1, \dots, x_{n-1}) = (\tilde{x}_0, \dots, \tilde{x}_d, x_1, \dots, x_n)$$

,

where  $\tilde{x}_0, \dots, \tilde{x}_d, x_1, \dots, x_{n-1} \in_R \mathbb{F}_2$  are chosen randomly and independently from  $\mathbb{F}_2$ , and

$$x_n = x \oplus \prod_{j=0}^d \tilde{x}_j \oplus \bigoplus_{i=1}^{n-1} x_i$$

.

Observe that our masking scheme is obtained from the ISW transformation by replacing the first share  $x_0$  in ISW by a non-linear sharing  $x_0 = \prod_{j=0}^d \tilde{x}_j$ . The unmasking function is defined as follows:

$$\operatorname{Decode}(\tilde{x}_0,\ldots,\tilde{x}_d,x_1,\ldots,x_n)=\prod_{j=0}^d \tilde{x}_j\oplus\bigoplus_{i=1}^n x_i.$$

The data transformation is followed by the transformations of each AND and XOR gate. Throughout the paper, we define the transformed gates as And and Xor (or And[n,d]) and Xor[n,d]) gadgets respectively.

## 3.1 Gate Transformations

In this section the generic constructions for the Xor and And gadgets are presented. Additionally, we provide definition of the RefreshMask gadget, which is needed to protect against algebraic attacks. The scheme can be used for an arbitrary order n of linear masking and any degree d of the non-linear component. Though the constructions are general, the algebraic security depends on the variable structure (details can be found in Section 4). Depending on the non-linear degree d, the following intermediate variables need a special structure:

- The intermediate variable  $\mathcal{U}$  used in Xor and specified in Equation (1),

- The intermediate variables  $r_{j,0}$  in Equation (2), used in And,

- The intermediate variables W and R used in RefreshMask, Equation (3).

In the following descriptions we first introduce the functionalities of these variables which can be defined for arbitrary orders of n and d. Afterwards, we will show the computational structure of these variables for d = 1 and d = 2.

Let x and y be two bits and consider an (n,d)-masking scheme, i.e. x and y have been split into (n+d+1) shares such that  $\prod_{j=0}^d \tilde{x}_j \oplus \bigoplus_{i=1}^n x_i = x$  and  $\prod_{j=0}^d \tilde{y}_j \oplus \bigoplus_{i=1}^n y_i = y$ .

**Xor**[n, d] **Gadget:** A masked representation of  $z = x \oplus y$  with n + d + 1 shares such that  $\prod_{i=0}^{d} \tilde{z}_{j} \oplus \bigoplus_{i=1}^{n} z_{i} = z$  can be calculated as follows:

**Step 0:** The input shares are processed by RefreshMask gadgets;

$$\overline{x} \leftarrow \texttt{RefreshMask}(\overline{x}) \text{ and } \overline{y} \leftarrow \texttt{RefreshMask}(\overline{y}).$$

**Step 1:** The values of the non-linear shares are processed:

$$\tilde{z}_i = \tilde{x}_i \oplus \tilde{y}_i \text{ for } 0 < i < d.$$

**Step 2:** Computation of linear shares:

$$z_i = \begin{cases} x_i \oplus y_i, & \text{for } 1 \le i < n \\ x_i \oplus y_i \oplus \mathcal{U}, & \text{for } i = n. \end{cases}$$

where the functionality of  $\mathcal{U}$  is defined as follows:

$$\mathcal{U} = \bigoplus_{\substack{I \subseteq \{0,\dots,d\}\\I \neq \emptyset}} \prod_{i \in I} \tilde{x}_i \prod_{j \notin I} \tilde{y}_j \tag{1}$$

Moreover, we can introduce the computational structure of  $\mathcal U$  for a secure masking scheme as follows:

- $\operatorname{Xor}[n,1]$ :  $\mathcal{U} = \tilde{x}_0 \tilde{y}_1 \oplus \tilde{x}_1 \tilde{y}_0$

- $\operatorname{Xor}[n,2]$ :  $\mathcal{U} = \tilde{x}_1(\tilde{x}_2\tilde{y}_0 \oplus \tilde{y}_2(\tilde{x}_0 \oplus \tilde{y}_0)) \oplus \tilde{y}_1(\tilde{x}_2\tilde{y}_0 \oplus \tilde{x}_0(\tilde{x}_2 \oplus \tilde{y}_2))$

- Xor[n, d] for  $d \geq 3$ , the functionality of  $\mathcal{U}$  can be defined as in Equation (1). However the computational structure should be described carefully in order not to create vulnerabilities in algebraic security.

```

Algorithm 1 Xor(\overline{x}, \overline{y})

```

```

Input: The shares \overline{x} = ((\tilde{x}_j)_{j \in [0,d]}, (x_i)_{i \in [1,n]}) and \overline{y} = ((\tilde{y}_j)_{j \in [0,d]}, (y_i)_{i \in [1,n]}).

Output: The shares of x \oplus y as \overline{z} = ((\tilde{z}_j)_{j \in [0,d]}, (z_i)_{i \in [1,n]}).

1: \overline{x} \leftarrow \text{RefreshMask}(\overline{x})

2: \overline{y} \leftarrow \text{RefreshMask}(\overline{y})

3: for 0 \le j \le d do

\tilde{z}_j \leftarrow \tilde{x}_j \oplus \tilde{y}_j

5: for 1 \le i < n do

z_i \leftarrow x_i \oplus y_i

7: z_n \leftarrow x_n \oplus y_n \oplus \mathcal{U}

8: return \bar{z} = ((\tilde{z}_j)_{j \in [0,d]}, (z_i)_{i \in [1,n]})

```

And [n, d] Gadget: A masked representation of z = xy with n + d + 1 shares such that  $\prod_{i=0}^{d} \tilde{z}_{i} \oplus \bigoplus_{i=1}^{n} z_{i} = z$  can be calculated as follows:

**Step 0:** The input shares are processed by RefreshMask gadgets;

$$\overline{x} \leftarrow \texttt{RefreshMask}(\overline{x}) \text{ and } \overline{y} \leftarrow \texttt{RefreshMask}(\overline{y}).$$

**Step 1:** The calculations of the values with multiplicative representation are processed. Additional random bits  $r^{i,j}$  are generated in order to attain algebraic security in the second step.

$$\tilde{z}_i = \tilde{x}_i \tilde{y}_{i'} \oplus r^{i,1} \oplus \cdots \oplus r^{i,n} \text{ for } 0 \leq i \leq d \text{ where } i' = i+1 \mod(d+1).$$

**Step 2:** The variables  $r_{j,i}$  for  $0 \le i < j \le n$  are generated as follows:

$$r_{j,i} = \begin{cases} (r_{i,j} \oplus (\tilde{x}_0 \cdots \tilde{x}_d) y_j) \oplus x_j (\tilde{y}_0 \cdots \tilde{y}_d), & \text{for } i = 0 \\ (r_{i,j} \oplus x_i y_j) \oplus x_j y_i, & \text{for } 1 \le i \le n \text{ where } r_{i,j} \in_R \mathbb{F}_2 \text{ (b) }, \end{cases}$$

The calculations for  $1 \le i \le n$  are processed as identical to the ISW-And gadget. However, for i = 0 the calculations require a special computational structure:

$$r_{i,0} = [r_{0,j} \oplus (\tilde{x}_0 \cdots \tilde{x}_d)y_j] \oplus x_j(\tilde{y}_0 \cdots \tilde{y}_d) \text{ for } 1 \le j \le n.$$

(2)

Observe that  $r_{i,j}$  for  $1 \le i < j \le n$  is assigned a uniformly random value. However,  $r_{0,j}$  cannot be assigned as random. Instead,  $r_{0,j}$  should be defined in such a way that the following equation holds:

$$\bigoplus_{j=1}^{n} r_{0,j} = \bigoplus_{\substack{I \subset \{0,\dots,d\}\\I \neq \emptyset}} \prod_{i \in I} \tilde{x}_i \tilde{y}_{i'} \prod_{j \notin I} (r^{j,1} \oplus \dots \oplus r^{j,n}) \text{ where } i' = i+1 \mod(d+1).$$

Throughout the paper we denote the right-hand side of the above equation as  $\mathcal{V}$ . Note that the above functionality for  $r_{i,0}$  (given on the right-hand side of Equation (2)) is not secure against an algebraic attack, even if it is only a first-order one. Below we provide a secure computational structure for the case of an (n, 1) and (n, 2)-masking.

• And

$$[n,1]: r_{j,0} = \tilde{x}_1(\tilde{x}_0y_j \oplus r^{0,j}\tilde{y}_0) \oplus \tilde{y}_1(\tilde{y}_0x_j \oplus r^{1,j}\tilde{x}_0) \oplus r^{1,j}(r^{0,1} \oplus \ldots \oplus r^{0,n}).$$

#### Algorithm 2 And $(\overline{x}, \overline{y})$

```

Input: The shares \overline{x} = ((\tilde{x}_j)_{j \in [0,d]}, (x_i)_{i \in [1,n]}) and \overline{y} = ((\tilde{y}_j)_{j \in [0,d]}, (y_i)_{i \in [1,n]}).

Output: The vector of shares of xy as \overline{z} = ((\tilde{z}_j)_{j \in [0,d]}, (z_i)_{i \in [1,n]}).

1: \overline{x} \leftarrow \text{RefreshMask}(\overline{x})

2: \overline{y} \leftarrow \text{RefreshMask}(\overline{y})

3: for 0 \le i \le d do

\triangleright i' = i + 1 \mod(d+1)

4:

\tilde{z}_i = \tilde{x}_i \tilde{y}_{i'}

for 1 \le j \le n do

r^{i,j} \leftarrow \mathtt{rand}(0,1)

6:

\tilde{z}_i = \tilde{z}_i \oplus r^{i,j}

7:

8: for 0 \le i \le n do

for i < j \le n do

9:

if i = 0 then

10:

r_{i,0} \leftarrow as described in the text.

11:

12:

r_{i,j} \leftarrow \mathtt{rand}(0,1)

13:

r_{j,i} \leftarrow (r_{i,j} \oplus x_i y_j) \oplus x_j y_i

14:

15: for 1 \le i \le n do

z_i \leftarrow x_i y_i

16:

for 0 \le j \le n and j \ne i do

17:

\triangleright Denoted by z_{i,j}

z_i \leftarrow z_i \oplus r_{i,j}

19: return \overline{z} = ((\tilde{z}_j)_{j \in [0,d]}, (z_i)_{i \in [1,n]})

```

```

\begin{split} \bullet \quad & \text{And}[n,2]: r_{j,0} = \tilde{x}_0 \left[ \tilde{x}_2(\tilde{x}_1 y_j \oplus r^{0,j} \tilde{y}_0) \oplus r^{1,j} v \tilde{y}_1 \right] \oplus \\ & \qquad \qquad \tilde{y}_0 \left[ \tilde{y}_1(\tilde{y}_2 x_j \oplus r^{1,j} \tilde{x}_2) \oplus r^{0,j} u \tilde{x}_2 \right] \oplus \\ & \qquad \qquad \tilde{x}_0 \tilde{y}_1(r^{1,j} \tilde{x}_2 \tilde{y}_0 \oplus r^{2,j} \tilde{x}_1 \tilde{y}_2) \oplus r^{0,j} \tilde{x}_1 \tilde{y}_2(v \oplus \tilde{x}_2 \tilde{y}_0) \oplus \\ & \qquad \qquad \tilde{x}_2 \tilde{y}_0(r^{0,j} \tilde{x}_0 \oplus r^{1,j} \tilde{y}_1) \oplus uvr^{0,j}. \end{split}  where u = r^{1,1} \oplus \cdots \oplus r^{1,n} and v = r^{2,1} \oplus \cdots \oplus r^{2,n}.

```

• And [n, d] for  $d \geq 3$  the circuit nodes that calculates  $r_{j,0}$  should be structured in such a way that algebraic security properties are satisfied.

**Step 3:** The final step can be performed identical to an ISW-And gadget: For every  $1 \le i \le n$ , compute  $z_i = x_i y_i \oplus \bigoplus_{i \ne j} r_{i,j}$ .

RefreshMask[n,d] Gadget: This operation has a crucial importance for generating an algebraically secure implementation. In fact, it has to be combined with each Xor and And gadget in order to obtain a fully secure masking scheme. The security details can be found in Section 4.

**Step 1:** For  $0 \le i \le d$ , calculate  $\tilde{x}'_i = \tilde{x}_i \oplus \tilde{r}_i$  where  $\tilde{r}_i \in_R \mathbb{F}_2$ .

**Step 2:** First initialize  $x_i' \leftarrow x_i$  for all  $i \in [1, n]$  and for  $1 \le i < j \le n$ , calculate  $x_i' = x_i' \oplus r_{i,j}$  and  $x_j' = x_j' \oplus r_{i,j}$  where  $r_{i,j} \in_R \mathbb{F}_2$ .

**Step 3:** In the last step we sample  $r_0 \in_R \mathbb{F}_2$  and define two intermediate variables as follows:

$$\mathcal{W}' = \bigoplus_{\substack{I \subsetneq \{0, \dots, d\}}} \prod_{i \in I} \tilde{x}_i \prod_{j \notin I} \tilde{r}_j \text{ and } \mathcal{W} = \bigoplus_{\substack{I \subsetneq \{0, \dots, d\} \\ I \neq \emptyset}} \prod_{i \in I} (\tilde{x}_i \oplus r_0) \prod_{j \notin I} \tilde{r}_j,$$

#### **Algorithm 3** RefreshMask $(\overline{x})$

```

Input: The shares \overline{x} = ((\tilde{x}_j)_{j \in [0,d]}, (x_i)_{i \in [1,n]})

Output: The shares \overline{x} = ((\tilde{x}'_j)_{j \in [0,d]}, (x'_i)_{i \in [1,n]})

1: for 0 \le j \le d do

2: \tilde{r}_j \leftarrow \text{rand}(0,1)

3: \tilde{x}'_j \leftarrow \tilde{x}_j \oplus \tilde{r}_j

4: for 1 \le i \le n do x'_i \leftarrow x_i

5: for 1 \le i \le n do

6: for i+1 \le j \le n do

7: r_{i,j} \leftarrow \text{rand}(0,1)

8: x'_i \leftarrow x'_i \oplus r_{i,j} \Rightarrow Denoted by a_{i,j}

9: x'_j \leftarrow x'_j \oplus r_{i,j} \Rightarrow Denoted by b_{j,i}

10: r_0 \leftarrow \text{rand}(0,1) \Rightarrow r_0 is used to compute \mathcal{W} and \mathcal{R}

11: x'_n \leftarrow x'_n \oplus \mathcal{W} \oplus \mathcal{R}

12: return (((\tilde{x}'_j)_{j \in [0,d]}, (x'_i)_{i \in [1,n]})

```

Here, as usual, a product over the empty set I is evaluated as 1. Using the above equations we define the variable  $\mathcal{R} = \mathcal{W} \oplus \mathcal{W}'$ . Now, we can introduce the variables that need to be added to the final share  $x_n$  as:

$$x'_n \leftarrow x'_n \oplus \mathcal{W} \oplus \mathcal{R} \text{ where } \mathcal{R} = \mathcal{W}' \oplus \mathcal{W}.$$

(3)

Remark that we cannot directly add  $\mathcal{W}'$  to the final share  $x_n$  due to algebraic security properties. Therefore, the variables  $\mathcal{W}$  and  $\mathcal{R}$  should be added to the final share in order to define an algebraically secure mask refreshing gadget. The computational structure of the circuit nodes to calculate  $\mathcal{W}$  and  $\mathcal{R}$  for RefreshMask[n,1] and RefreshMask[n,2] can be found below.

- RefreshMask $[n,1]: \mathcal{W} = \tilde{r}_0(\tilde{x}_1 \oplus r_0) \oplus \tilde{r}_1(\tilde{x}_0 \oplus r_0) \text{ and } \mathcal{R} = (\tilde{r}_0 \oplus r_0)(\tilde{r}_1 \oplus r_0) \oplus r_0.$

- RefreshMask $[n,2]: \mathcal{W} = [\tilde{r}_2(\tilde{x}_0 \oplus r_0)][\tilde{r}_1 \oplus (\tilde{x}_1 \oplus r_0)] \oplus [\tilde{r}_1(\tilde{x}_2 \oplus r_0)][\tilde{r}_0 \oplus (\tilde{x}_0 \oplus r_0)] \oplus [\tilde{r}_0(\tilde{x}_1 \oplus r_0)][\tilde{r}_2 \oplus (\tilde{x}_2 \oplus r_0)]$   $\mathcal{R} = (\tilde{r}_0 \oplus r_0)(\tilde{r}_1 \oplus r_0)(\tilde{r}_2 \oplus r_0) \oplus r_0[\tilde{r}_2(\tilde{x}_0 \oplus r_0) \oplus \tilde{r}_1(\tilde{x}_0 \oplus r_0) \oplus \tilde{r}_0(\tilde{x}_1 \oplus r_0)] \oplus r_0[\tilde{r}_2(\tilde{x}_1 \oplus r_0) \oplus \tilde{r}_1(\tilde{x}_2 \oplus r_0) \oplus \tilde{r}_0(\tilde{x}_2 \oplus r_0)].$

- RefreshMask[n,d] for  $d \geq 3$  the circuit nodes that calculate W and R should be constructed in such a way that algebraic security properties are satisfied.

### 3.2 Correctness and Performance Analysis

Next, we introduce the transformation  $\mathtt{T}^{(n,d)}$  to generate a Boolean circuit that is protected by an (n,d)-masking scheme by using the gadgets described in Section 3.1. The following lemma summarizes the correctness of the transformation  $\mathtt{T}^{(n,d)}$ .

**Lemma 1.** Let us denote the Boolean circuit C initialized with data D by C[D]. The transformation  $T^{(n,d)}:C[D]\mapsto C'[D']$  where C' uses And, Xor, RefreshMask gadgets and Encoding, Decoding functions described in Section 3 with randomness gates is a functionality preserving transformation, i.e. C[D] and C'[D'] have the same input-output behavior.

**Table 1:** The number of bitwise operations in a masked Xor, And and RefreshMask (or RefM in short) gadget. Remark that (n,0)-masking scheme corresponds to ISW gadgets. The last part of the table corresponds to the overhead of (n,d)-masking scheme compared to the ISW transformation.

|                               | Xor                                              | And                             | Randomness         |  |  |  |

|-------------------------------|--------------------------------------------------|---------------------------------|--------------------|--|--|--|

| Xor[n,0]                      | n+1                                              | -                               | -                  |  |  |  |

| $\mathtt{And}[n,0]$           | 2n(n+1)                                          | $(n+1)^2$                       | n(n+1)/2           |  |  |  |

| $\mathtt{RefM}[n,0]$          | n(n-1)                                           | -                               | n(n-1)/2           |  |  |  |

| Xor[n,1]                      | n+4                                              | 2                               | -                  |  |  |  |

| $\mathtt{And}[n,1]$           | $2n^2 + 5n - 1$                                  | $n^2 + 7n + 2$                  | n(n+3)/2           |  |  |  |

| $\mathtt{RefM}[n,1]$          | n(n-1) + 8                                       | 3                               | (n(n-1)/2) + 2     |  |  |  |

| Xor[n,2]                      | n+9                                              | 6                               | -                  |  |  |  |

| $\mathtt{And}[n,2]$           | $2n^2 + 15n - 2$                                 | $n^2 + 27n + 3$                 | n(n+5)/2           |  |  |  |

| $\mathtt{RefM}[n,2]$          | n(n-1) + 26                                      | 16                              | (n(n-1)/2) + 3     |  |  |  |

| Xor[n,d]                      | $n+d+2+\mathcal{U}_x$                            | $\mathcal{U}_a$                 | -                  |  |  |  |

| $\mathtt{And}[n,d]$           | $n(2n+d-1)+\mathcal{V}_x$                        | $n^2 + d + 1 + \mathcal{V}_a$   | n(n+2d+1)/2        |  |  |  |

| $\mathtt{RefM}[n,d]$          | $n(n-1) + d + 1 + \mathcal{W}_x + \mathcal{R}_x$ | $\mathcal{W}_a + \mathcal{R}_a$ | (n(n-1)/2) + d + 1 |  |  |  |

| Overhead                      |                                                  |                                 |                    |  |  |  |

| $\mathtt{Xor}[n,d]$           | $d+1+\mathcal{U}_x$                              | $\mathcal{U}_a$                 | -                  |  |  |  |

| ${\tt And}[n,d]$              | $n(2n+d-3)+\mathcal{V}_x-1$                      | $d + \mathcal{V}_a - n$         | nd                 |  |  |  |

| $\mathtt{RefM}[n,d]$          | $d+1+\mathcal{W}_x+\mathcal{R}_x$                | $\mathcal{W}_a + \mathcal{R}_a$ | d+1                |  |  |  |

| $\frac{\texttt{RefM}[n,d]}{}$ | $d+1+\mathcal{W}_x+\mathcal{R}_x$                | $W_a + \mathcal{R}_a$           | d+1                |  |  |  |

The proof for this lemma can be found in Appendix A. In conclusion, the transformation  $T^{(n,d)}$  can be used to transform any circuit to an (n,d)-masked circuit in a functionality preserving manner. Although we are using an  $n^{th}$  order linear masking, the scheme only provides an  $(n-1)^{th}$  probing security. Due to the non-linear sharing, the masking loses one share to increase the decoding order. The algebraic security depends on the structure of Equations (1), (2), and (3) in each gadget as discussed above. Further details can be found in Section 4.2.

**Performance Analysis:** In order to compare our construction with the previous schemes, we analyze the performance of our scheme in terms of bitwise operations and randomness requirements. An analytical comparison of different orders and a comparison between the ISW transformation and (n,d)-masking scheme can be found in Table 1.

In the following analysis, for simplicity, we use the symbol vertical bar (|) to separate the number of Xor, And operations respectively. We exclude the RefreshMask gadgets inside the Xor and And gadgets to analyze the constructions straightforwardly. Since the structure of the special variables depends on the non-linear degree d, we use a symbolic approach to analyze the performance numbers for the higher orders (i.e. for  $d \geq 3$ ). We use subscripts to denote the number of operations within  $\mathcal{U}$ ,  $\mathcal{V}$ ,  $\mathcal{W}$ , and  $\mathcal{R}$ , e.g.,  $\mathcal{U}_x$  and  $\mathcal{U}_a$  represent the number of bitwise Xor, And operations within  $\mathcal{U}$  respectively.

As seen in Table 1, the Xor gadget can be transformed efficiently. The cost of the gadget in the ISW transformation is n+1 bitwise Xor operations while an (n,d)-masking requires n+d+2 bitwise Xor operations and the additional cost of the variables  $\mathcal{U}$ . Therefore, the cost of the Xor gadget can be calculated as;  $(n+d+2+\mathcal{U}_x)|\mathcal{U}_a$ .

The cost of an And gadget can be analyzed easily by comparing it step-by-step with the ISW transformation. As seen in the construction in Section 3, the gadget can be divided into three stages.

- Step 1 requires n(d+1) random bits; the cost of processing these values can be calculated as n(d+1)|d+1.

- Step 2(a) includes the calculations of  $r_{j,0}$  for  $1 \leq j \leq n$ . For the (n,1) masking,  $\mathcal{V}_x = 4n$  and  $\mathcal{V}_a = 7n$ . Additionally, the calculations of  $r^{0,1} \oplus \ldots \oplus r^{0,n}$  require n-1 Xor operations. Similarly, for the (n,2) masking, we get  $\mathcal{V}_x = 12n$  and  $\mathcal{V}_a = 27n$ . The intermediate variables u, v, and uv are calculated only once and they require 2(n-1)|1 gates.

- Step 2(b) & Step 3 involve the calculations of  $r_{j,i}$  for  $1 \le i < j \le n$ ,  $i \ne 0$  and Step 3. These parts can be processed identical to the ISW transformation and cost  $2n(n-1)|n^2$  gates, while the required number of random bits is n(n-1)/2. Observe that the cost of these parts are exactly the cost of an ISW-AND gadget with n shares.

To sum up, we express the cost of And[n,d] gadget as  $(n(2n+d-1)+\mathcal{V}_x)|(n^2+d+1+\mathcal{V}_a)$  gates, and the required randomness as n(n+2d+1)/2.

We analyze the performance of the RefreshMask gadget using a similar methodology. The total amount of required randomness and the number of required bitwise Xor operations can be calculated as (n(n-1)/2) + d + 1 and n(n-1) + d + 1 respectively. As in the previous gadgets, the calculations of  $\mathcal{W}$  and  $\mathcal{R}$  add more calculations to the structure. The numbers for RefreshMask[n, 1] and RefreshMask[n, 2] are given in Table 1.

Using the performance analysis, we show the exact overhead of our scheme. The numbers in the overhead section of Table 1 can be calculated by comparing the cost of the  $n^{th}$ -order ISW transformation with an (n,d)-masking scheme. As seen in the table, the cost principally depends on the calculation of the values  $\mathcal{U}$ ,  $\mathcal{V}$ ,  $\mathcal{W}$ , and  $\mathcal{R}$ , while the randomness is affected by the masking degrees n and d.

# 4 Security Against Computational and Algebraic Attacks

In this section, we prove that our proposed [n,d] masking scheme resists both computational and algebraic attacks, up to  $(n-1)^{th}$  order and  $d^{th}$  order, respectively. We use the definition of non-interference as defined in [BBD<sup>+</sup>16], which guarantees security against t probes for  $t \leq n$  as proposed by Ishai et al. [ISW03], and the definition of security against algebraic attacks of order d as proposed in [BU18]. First, we recall briefly both security notions and then we prove that our (n,d) construction is secure against probing up to order n-1 and against algebraic attacks for d=1 and d=2. Remark that probing security implies security against computational attacks of the same order, since computational attacks correspond to side-channel attacks of the same order [BRVW19].

# 4.1 Security Notions

We first cover the security notions that we used to prove our security properties, starting with probing security. Roughly speaking, in the setting of the probing model, an adversary may invoke the (randomized) construction multiple times and adaptively choose the inputs. Prior to each invocation, the adversary may fix an arbitrary set of  $t \leq n$  wires of the circuit values which can be observed during that invocation.

The security against t probes requires the existence of a simulator [ISW03]. The simulator attempts to simulate the view of the adversary using only black-box access (i.e., without having access to any internal wires) to the transformed circuit C'. The presence of a simulator (or simulatability) implies that t probes are indeed independent of the processed data and therefore t probes will not provide any information to the adversary. In this paper we use a more refined security model, t-non-interference (t-NI) and t-strong non-interference (t-SNI), as defined in [BBD<sup>+</sup>16]. We use the restatements of the definitions by Coron et al. [CGPZ16].

**Definition 1** (t-NI Security). Let G be a gadget which takes as input n+1 shares  $(x_i)_{0 \le i \le n}$  and outputs n+1 shares  $(y_i)_{0 \le i \le n}$ . The gadget G is said to be t-NI secure if for any set of  $t_1$  probed intermediate variables and any subset  $\mathcal{O} \subset [0, n]$  of output indices, such that  $t_1 + |\mathcal{O}| \le t$ , there exists a subset  $I \subset [0, n]$  of input indices which satisfies  $|I| \le t_1 + |\mathcal{O}|$ , such that the  $t_1$  intermediate variables and the output variables  $y_{|\mathcal{O}}$  can be perfectly simulated from  $x_{|I|}$ .

**Definition 2** (t-SNI Security). Let G be a gadget which takes as input n+1 shares  $(x_i)_{0 \le i \le n}$  and outputs n+1 shares  $(y_i)_{0 \le i \le n}$ . The gadget G is said to be t-SNI secure if for any set of  $t_1$  probed intermediate variables and any subset  $\mathcal{O} \subset [0,n]$  of output indices, such that  $t_1 + |\mathcal{O}| \le t$ , there exists a subset  $I \subset [0,n]$  of input indices which satisfies  $|I| \le t_1$ , such that the  $t_1$  intermediate variables and the output variables  $y_{|\mathcal{O}}$  can be perfectly simulated from  $x_{|I|}$ .

The main difference between the t-NI and t-SNI security notions is that in the latter notion the size of the input subsets I does not depend on the size of the set of probed output shares  $\mathcal{O}$ . Thus, the t-SNI security notion ensures input-output separation, which is an essential component for composability of the gadgets.

Note that security in the probing model is a necessary but not a *sufficient* condition for a secure white-box implementation, as probing secure implementations may still be vulnerable to algebraic attacks. To prevent algebraic attacks, *prediction security* is also necessary.

**Definition 3** (Prediction Security (*d*-PS), [BU18]). Let  $C: \mathbb{F}_2^{N'} \times \mathbb{F}_2^{R_C} \to \mathbb{F}_2^M$  be a Boolean circuit that takes N'-bit inputs, uses  $R_C$  random bits, and produces an M-bit output. Let  $E: \mathbb{F}_2^N \times \mathbb{F}_2^{R_E} \to \mathbb{F}_2^{N'}$  be an arbitrary function that takes N-bit input, uses  $R_E$  random bits, and produces an N'-bit output. Consider the following security experiment with an adversary  $\mathcal{A}$ , an integer  $d \geq 1$ , and a predetermined variable  $b \in \{0,1\}$ :

```

Algorithm 4 PS^{C,E,d}(A,b)

```

```

1: (\tilde{f}, \overline{x}^{[0]}, \overline{x}^{[1]}, \tilde{y}, b) \leftarrow \mathcal{A}(C, E, d) where \tilde{f} \in \mathcal{F}^{(d)}(C), (\overline{x}^{[l]} = (x_1^{[l]}, \dots, x_Q^{[l]}))_{l \in \{0,1\}}, x_i^{[l]} \in \mathbb{F}_2^N, \ \tilde{y} \in \mathbb{F}_2^Q \text{ and } l \in \{0,1\}

2: (r_1, \dots, r_Q) \in_R (\mathbb{F}_2^{R_E})^Q

3: (\tilde{r}_1, \dots, \tilde{r}_Q) \in_R (\mathbb{F}_2^{R_C})^Q

4: for f \in \mathcal{F}^{(d)}(C) do

5: y(f) = (f(E(x_1^{[b]}, r_1), \tilde{r}_1), \dots, f(E(x_Q^{[b]}, r_Q), \tilde{r}_Q))

6: F \leftarrow \{f \in \mathcal{F}^{(d)}(C) \mid y(f) = \tilde{y}\}

7: if F = \{\tilde{f}\} then return 1 else return 0

```

Finally, we define the advantage of an adversary  $\mathcal{A}$  as

$$\mathrm{Adv}^{\mathrm{PS}}_{C,E,d}[\mathcal{A}] \ = \ \left| \Pr[\mathrm{PS}^{C,E,d}(\mathcal{A},0) = 1] - \Pr[\mathrm{PS}^{C,E,d}(\mathcal{A},1) = 1] \right|.$$

The pair (C, E) is said to be  $d^{th}$  order prediction-secure (d-PS) if for any adversary  $\mathcal A$  the advantage is negligible.

In summary, prediction security analyzes the behavior of functions from  $\mathcal{F}^{(d)}(C)$  composed with an encoding function E. Consider two elements  $x, x' \in \mathbb{F}_2^N$ , if an adversary is able to find a function  $f \in \mathcal{F}^{(d)}(C) \setminus \{\mathbf{0}, \mathbf{1}\}$  such that  $f(E(x, \cdot), \cdot)$  is constant (or highbias) but  $f(E(x', \cdot), \cdot)$  is non-constant (or low-bias) then the adversary can distinguish these inputs and therefore the pair (C, E) is considered insecure. Thus, prediction security requires every function from the set  $\mathcal{F}^{(d)}(C)$  to have low-bias.

The outline of the security analysis can be summarized as follows. First our gadgets and encoding function have been proven to satisfy  $\epsilon$ -1-AS, i.e. Definition 6 and Definition 7 (resp.  $\epsilon$ -2-AS Definition 8 and Definition 9). To show that a gadget (or an encoding function) satisfies the corresponding definition, we analyze the bias of functions  $f \in \mathcal{F}^{(d)}(C) \setminus \{0,1\}$  where d=1 or 2. The  $\epsilon$ -1-AS definition implies that f is either an affine function of inputs or f has low bias when the input is fixed, i.e. when f is a function of random values with a constant input. Similarly,  $\epsilon$ -2-AS implies that f is either a second-order combination of affine functions of input and circuit nodes or f has low bias when the input is fixed, i.e. when f is a function of random values with a constant input.

The proofs of individual gadgets and encoding functions are followed by the composability results. The composability of 1-AS gadgets is proven as in [BU18]. On the other hand the composability of 2-AS gadgets are extended in a non-trivial way and the composability of 2-AS gadgets are given in two fold; an arbitrary combination of two gadgets operated in parallel order (Proposition 10) and in sequential order (Proposition 11). Since the former analysis includes the linear combination of the nodes, a straightforward approach is enough to prove the composability. In our approach, we need to check the non-linear combinations of circuit nodes within the different gadgets.

Using the above steps, an arbitrary circuit, generated by And[n,d], Xor[n,d] and RefreshMask[n,d] gadgets for d=1 and d=2 are shown to satisfy algebraic security definitions respectively.

Next we prove the composability of an arbitrary circuit C with an encoding function E in Propositions 7 and 12 and show that  $C(E(\cdot))$  satisfies algebraic security definitions respectively. This implies that every function from the set  $\mathcal{F}^d(C(E(\cdot)))$  has bias  $\leq \epsilon$ .

However to achieve prediction security we need a better security bound than  $\epsilon$ . To prove that a circuit is prediction secure we need to show that  $\operatorname{Adv}_{C,E,d}^{\operatorname{PS}}[\mathcal{A}] \leq 2^{-\kappa}$  depending on a security parameter  $\kappa$  and this can be achieved by adding  $\operatorname{dummy}$  random nodes to the circuit. Using the maximum bias bound  $\epsilon$ , the required number  $\operatorname{dummy}$  random bits to achieve a security bound  $\kappa$  is restated in Proposition 1.

In [BU18], it is shown that a circuit C achieves d-PS, if there are enough random bits used in the circuit depending on the bias bound. Before giving the relation between random bits and d-PS, we first remark the set of functions that is needed for the analysis.

**Definition 4** ([BU18]). Let  $C(\overline{x}', \overline{r}_c) : \mathbb{F}_2^{N'} \times \mathbb{F}_2^{R_C} \to \mathbb{F}_2^M$  be a Boolean circuit,  $E(\overline{x}, \overline{r}_e) : \mathbb{F}_2^N \times \mathbb{F}_2^{R_E} \to \mathbb{F}_2^{N'}$  an arbitrary function and  $d \geq 1$  an integer. For any function  $f \in \mathcal{F}^{(d)}(C) \setminus \{0, 1\}$  and for any  $\overline{x} \in \mathbb{F}_2^N$  define  $f_{\overline{x}} : \mathbb{F}_2^{R_E} \times \mathbb{F}_2^{R_C} \to \mathbb{F}_2$  given by  $f_{\overline{x}}(\overline{r}_e, \overline{r}_c) = f(E(\overline{x}, \cdot), \cdot)$  and denote the set of all such functions as  $\mathcal{R}_d$ :

$$\mathcal{R}_d = \{ f_{\overline{x}}(\overline{r}_e, \overline{r}_c) \mid f \in \mathcal{F}^{(d)}(C) \setminus \{\mathbf{0}, \mathbf{1}\}, \overline{x} \in \mathbb{F}_2^N \}.$$

Using the above definition, a bound for the d-PS is given as in the following proposition which indicates the required number of random bits.

**Proposition 1** (Corollary 1 in [BU18]). Let  $\epsilon$  be the maximum bias among all functions from  $\mathcal{R}_d$ , i.e.,  $\epsilon = \max_{f_{\overline{x}} \in \mathcal{R}_d} \mathcal{E}(f_{\overline{x}})$ . Let  $e = -\log_2(1/2 + \epsilon)$  and  $\kappa$  be a security parameter. Then for any adversary  $\mathcal{A}$  choosing vector size of Q:

$$Adv_{C,E,d}^{PS}[\mathcal{A}] \leq 2^{-\kappa}$$

if

$$e > 0$$

and  $R_C \ge \kappa \cdot (1 + 1/e)$ .

Although it may seem that prediction security covers probing security (or vice versa), both notions are in fact *incomparable*. Therefore, both notions are needed to analyze a secure white-box implementation. To illustrate the incomparability of the two notions, let us consider two examples; a white-box implementation protected with an  $n^{th}$ -order Boolean masking and minimalist quadratic masking defined in [BU18].

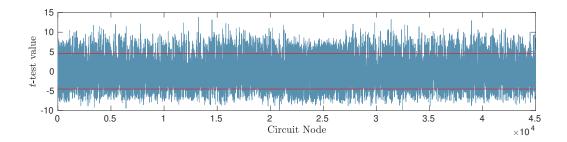

**Figure 1:** A first-order leakage detection on a circuit that simulates AES-128 with the masking defined in [BU18]. Clearly, the t-test value exceeds the threshold values shown by red lines.

**Example 1** (Probing Secure Masking Vulnerable to Algebraic Attacks). Applying an ISW transformation to the circuit and the data results in an  $n^{th}$ -order probing secure implementation. However, a first-order algebraic attack can exploit a first-order (linear) combination of intermediate values which is equal to a predictable value. Therefore, an  $n^{th}$ -order Boolean masking is secure in the probing model, but not secure in prediction security, as shown in [BU18].

**Example 2** (Algebraically secure masking vulnerable to probing). As the second example, we use the encoding function  $\operatorname{Encode}(x,x_0,x_1)=(x_0,x_1,x_0x_1\oplus x)$ . As given in [BU18], the masking scheme satisfies first-order algebraic security. However, it is not probing secure, not even first-order probing secure. A leakage is caused by the *unbalanced* sharing where the third share  $x_0x_1\oplus x$  statistically depends on the sensitive variable x. For any value x we have  $\Pr_{x_0,x_1\in_R\mathbb{F}_2}[(x_0x_1\oplus x)=x]=3/4$ . Thus, there exists no first-order function that is equal to a predictable vector, but there exists one node (the last share) that is highly correlated with a predictable vector.

To practically verify this leakage, we implement a basic bitwise AES-128 circuit using the Sbox designed by Boyar and Peralta [BP09] and implement a basic leakage detection test using 500 traces with 45000 nodes (N=500 and M=45000). As seen in Figure 1, the test shows intense leakage. The details of the experimental setup regarding the leakage detection, trace collection and the variable selection can be found Section 5.1.

As illustrated in Example 1, prediction security is based on finding a degree-d function whose output equals to a predictable value. However, in probing we only need to find a set of variables which depends on a predictable value, as shown in Example 2. Thus, we need to prove the security of our scheme in two steps:

- 1. Prove probing security using Definitions 1 and 2 for an arbitrary (n,d) scheme,

- 2. Prove prediction security using Definition 3 for (n,1) and (n,2) schemes.

#### 4.2 Security Against Computational Attacks in the Probing Model

We first provide some auxiliary definitions that form the basis of our security proofs.

**Definition 5** ((n,d)-family of shares). A vector  $\overline{x} = (\tilde{x}_0, \dots, \tilde{x}_d, x_1, \dots, x_n)$  of n+d+1 intermediate variables is called an (n,d)-family of shares if every tuple of the form  $((\tilde{x}_i)_{i\in \tilde{I}}, (x_i)_{i\in I})$  such that  $|\tilde{I}| \leq d+1$  and  $|I| \leq n-1$  of  $\tilde{x}_0, \dots, \tilde{x}_d, x_1, \dots, x_n$  is uniformly distributed and independent of any sensitive variable where  $x = \prod_{j=0}^d \tilde{x}_j \oplus \bigoplus_{i=1}^n x_i$  is a sensitive variable.

We can extend the definition as: two (n,d)-families of shares  $\overline{x} = (\tilde{x}_0 \dots, \tilde{x}_d, x_1, \dots, x_n)$  and  $\overline{y} = (\tilde{y}_0 \dots, \tilde{y}_d, y_1, \dots, y_n)$  are called to be (n-1)-independent of one another if every tuple composed of  $((\tilde{x}_i)_{i \in \overline{I}}, (x_i)_{i \in I})$  and  $((\tilde{y}_j)_{j \in \overline{J}}, (y_j)_{j \in J})$  with  $|\tilde{I}|, |\tilde{J}| \leq d+1$  and  $|I|, |J| \leq n-1$  is uniformly distributed and independent of any sensitive variable. Two (n,d)-families are (n-1)-dependent of one another if they are not (n-1)-independent.

To prove security of our scheme in the t-SNI notion, we decompose C into basic components, which we call randomized elementary transformations (or gadgets). Such a component gets as input two (n-1)-independent (n,d)-families of shares, resp. one (n,d)-family of shares, and it returns a (n,d)-family of shares.

In this section, we first prove that the randomized elementary transformations specified as in Algorithms 1, 2, and 3 satisfy non-interference notions. One challenge for proving t-SNI security results from the fact that in the proposed sharing only a subset of shares is uniformly distributed. The product of non-linear shares  $x_0$  (as expressed by  $x_0 = \prod_{j=0}^d \tilde{x}_j$ ) is non-uniformly distributed or biased. Hence,  $x_0$  can be predicted correctly by an adversary with high probability. Thus, the non-linear shares do not contribute to probing security. To address this fact, we consider the non-linear shares as public values accessible by the adversary or as  $free\ probes$ , due to the bias of their product. We use the following fact in our proofs.

Fact 1. Let G be a masked operation that operates on an (n,d)-family of shares  $\overline{x} = (\tilde{x}_0, \ldots, \tilde{x}_d, x_1, \ldots, x_n)$  (or two (n,d)-families of shares  $\overline{x} = (\tilde{x}_0, \ldots, \tilde{x}_d, x_1, \ldots, x_n)$  and  $\overline{y} = (\tilde{y}_0, \ldots, \tilde{y}_d, y_1, \ldots, y_n)$ ) as defined in Definition 5. A simulator can access non-linear shares  $(\tilde{x}_0, \ldots, \tilde{x}_d)$  (or  $(\tilde{x}_0, \ldots, \tilde{x}_d)$  and  $(\tilde{y}_0, \ldots, \tilde{y}_d)$ ) as free probes or public inputs to the gadgets.

Now we are ready to prove the security of our basic constructions. We start with the t-SNI property of the RefreshMask and And gadgets. Then, we continue with the t-NI property of the Xor gadget. The proofs can be found in Appendix A.

**Proposition 2.** (t-SNI of RefreshMask) Let  $\overline{x}=(\tilde{x}_0,\ldots,\tilde{x}_d,x_1,\ldots,x_n)$  be an (n,d)-family of shares, with  $n\geq 2$ , as input of Algorithm 3 to refresh masking. Then every tuple of  $t_1$  intermediate variables and  $t_2$  output variables in Algorithm 3 such that  $t_1+t_2\leq t$  can be simulated by at most  $t_1$  linear shares taken from  $\overline{x}$ .

**Proposition 3.** (t-SNI of And) Let  $\overline{x} = (\tilde{x}_0, \ldots, \tilde{x}_d, x_1, \ldots, x_n)$  and  $\overline{y} = (\tilde{y}_0, \ldots, \tilde{y}_d, y_1, \ldots, y_n)$  be two (n-1)-independent (n,d)-families of shares, with  $n \geq 2$ , inputs of Algorithm 2 for And. Then every tuple of  $t_1$  intermediate variables and  $t_2$  output variables such that  $t_1 + t_2 \leq t$  can be simulated by at most  $t_1$  linear shares taken from  $\overline{x}$  and  $\overline{y}$ .

**Proposition 4.** (t-NI of Xor) Let  $\overline{x} = (\tilde{x}_0, \dots, \tilde{x}_d, x_1, \dots, x_n)$  and  $\overline{y} = (\tilde{y}_0, \dots, \tilde{y}_d, y_1, \dots, y_n)$  be two (n-1)-independent (n,d)-families of shares, with  $n \geq 2$ , as input of Algorithm 1 to compute Xor. Then every tuple of  $t_1$  intermediate variables and  $t_2$  output variables such that  $t_1 + t_2 \leq t$  can be simulated by at most  $t_1 + t_2$  linear shares taken from  $\overline{x}$  and  $\overline{y}$ .

In conclusion, we prove the security against t probes of our individual gadgets such that t < n. Next, we analyze an arbitrary circuit C as a combination of our gadgets. As stated in [BBD<sup>+</sup>16], an algorithm is said to be t-NI if all gadgets are t-NI and every non-linear usage of a secret state is guarded by t-SNI refreshing gadgets. Moreover, it is sufficient to make the algorithm t-SNI, if every input or the output of a t-NI gadget is processed by a t-SNI gadget. Since the RefreshMask operation is proven to be secure in the t-SNI notion, we can use the operation defined in Section 3.1 to generate an arbitrary circuit that is secure against  $(n-1)^{th}$ -order probing attacks and therefore secure against  $(n-1)^{th}$ -order computational attacks.

**Table 2:** A summary of SNI/NI/Probing security verification of our gadgets. The inputs of an (n,d) gadget are two (n-1)-independent families of shares  $\bar{x}$  and  $\bar{y}$  (resp. one (n-1)-independent families of shares  $\bar{x}$  for RefreshMask or RefM in short). The number of observations (#Obs.) represents the total number of (intermediate and output) variables within the specified gadget. The timing corresponds to the total time for MaskVerif to verify the SNI, NI and probing security notions, respectively.

|                      | Free Probes                                                                        | # Obs. | SNI    | NI       | Probing  |

|----------------------|------------------------------------------------------------------------------------|--------|--------|----------|----------|

| $\mathtt{RefM}[2,1]$ | $[	ilde{x}_0,	ilde{x}_1]$                                                          | 23     | 0.01s  | 0.01s    | 0.01s    |

| $\mathtt{Xor}[2,1]$  | $[\tilde{x}_0, \tilde{x}_1], [\tilde{y}_0, \tilde{y}_1]$                           | 16     | -      | 0.01s    | 0.05s    |

| $\mathtt{And}[2,1]$  | $[\tilde{x}_0, \tilde{x}_1], [\tilde{y}_0, \tilde{y}_1]$                           | 52     | 0.01s  | 0.01s    | < 0.01 s |

| RefM[3,1]            | $[\tilde{x}_0, \tilde{x}_1]$                                                       | 30     | 0.01s  | 0.01s    | 0.01s    |

| $\mathtt{Xor}[3,1]$  | $[\tilde{x}_0, \tilde{x}_1], [\tilde{y}_0, \tilde{y}_1]$                           | 19     | -      | 0.01s    | 0.01s    |

| $\mathtt{And}[3,1]$  | $[\tilde{x}_0, \tilde{x}_1], [\tilde{y}_0, \tilde{y}_1]$                           | 86     | 0.02s  | 0.02s    | 0.02s    |

| RefM[4,1]            | $[\tilde{x}_0, \tilde{x}_1]$                                                       | 40     | 0.02s  | 0.01s    | <0.01s   |

| $\mathtt{Xor}[4,1]$  | $[\tilde{x}_0, \tilde{x}_1], [\tilde{y}_0, \tilde{y}_1]$                           | 22     | -      | 0.01s    | 0.01s    |

| $\mathtt{And}[4,1]$  | $[\tilde{x}_0, \tilde{x}_1], [\tilde{y}_0, \tilde{y}_1]$                           | 123    | 0.06s  | 0.05s    | 0.05s    |

| $\mathtt{RefM}[5,1]$ | $[	ilde{x}_0,	ilde{x}_1]$                                                          | 53     | 0.05s  | 0.01s    | 0.01s    |

| ${	t Xor}[5,1]$      | $[\tilde{x}_0, \tilde{x}_1], [\tilde{y}_0, \tilde{y}_1]$                           | 48     | -      | 0.01s    | 0.01s    |

| $\mathtt{And}[5,1]$  | $[\tilde{x}_0, \tilde{x}_1], [\tilde{y}_0, \tilde{y}_1]$                           | 170    | 2.25s  | 0.59s    | 0.45s    |

| RefM[2,2]            | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2]$                                          | 49     | 0.01s  | 0.01s    | 0.01s    |

| $\mathtt{Xor}[2,2]$  | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2], [\tilde{y}_0, \tilde{y}_1, \tilde{y}_2]$ | 24     | -      | < 0.01 s | 0.01s    |

| $\mathtt{And}[2,2]$  | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2], [\tilde{y}_0, \tilde{y}_1, \tilde{y}_2]$ | 98     | 0.02s  | 0.01s    | 0.01s    |

| RefM[3,2]            | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2]$                                          | 56     | 0.01s  | 0.01s    | 0.01s    |

| ${	t Xor}[3,2]$      | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2], [\tilde{y}_0, \tilde{y}_1, \tilde{y}_2]$ | 27     | -      | 0.01s    | 0.01s    |

| $\mathtt{And}[3,2]$  | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2], [\tilde{y}_0, \tilde{y}_1, \tilde{y}_2]$ | 154    | 0.03s  | 0.01s    | 0.02s    |

| RefM[4,2]            | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2]$                                          | 66     | 0.02s  | 0.01s    | 0.01s    |

| $\mathtt{Xor}[4,2]$  | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2], [\tilde{y}_0, \tilde{y}_1, \tilde{y}_2]$ | 30     | -      | 0.01s    | 0.01s    |

| $\mathtt{And}[4,2]$  | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2], [\tilde{y}_0, \tilde{y}_1, \tilde{y}_2]$ | 215    | 0.61s  | 0.08s    | 0.07s    |

| RefM[5,2]            | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2]$                                          | 79     | 0.04s  | 0.01s    | 0.01s    |

| $\mathtt{Xor}[5,2]$  | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2], [\tilde{y}_0, \tilde{y}_1, \tilde{y}_2]$ | 33     | -      | 0.01s    | 0.01s    |

| $\mathtt{And}[5,2]$  | $[\tilde{x}_0, \tilde{x}_1, \tilde{x}_2], [\tilde{y}_0, \tilde{y}_1, \tilde{y}_2]$ | 284    | 10.47s | 1.06s    | 1.11s    |

**Experimental Verification:** To support the results, we provide an experimental verification of the gadgets And[n,d], Xor[n,d] and RefreshMask[n,d] for d=1 and 2 and for n=1,2,3,4 and 5 using MaskVerif [BBC<sup>+</sup>19]. We implement our masking scheme (with the given orders n and d) inside the tool and experimentally verify the security features of our gadgets. The implementation of our scheme that can be used with MaskVerif is available as open source  $^2$ . The experiments are run on an Intel Core i5-6400 CPU@ 2.70GHz. A summary of the experimental results is given in Table 2.

# 4.3 Algebraic Security of the (n, 1)-Masking Scheme

In this section, we analyze the first order prediction security (Def. 3) of our (n,1)-masking scheme using the gadgets from Section 3.1. We proceed as follows. For our encoding function E and any Boolean circuit C constructed from our gadgets, we estimate  $\epsilon = \max_{f_{\overline{x}} \in \mathcal{R}_1} \mathcal{E}(f_{\overline{x}})$  – the maximum bias over all functions in the set  $\mathcal{R}_1$  specified in Definition 4, with d=1. We show that  $\epsilon$  is small. The bound on the prediction security of the (n,1)-masking, we get combining this bias with the upper bound on 1-PS shown in Proposition 1:  $\operatorname{Adv}_{C,E,d}^{\operatorname{PS}}[\mathcal{A}] \leq 2^{-\kappa}$ , assuming  $e=-\log_2(1/2+\epsilon)>0$  and the number of random bits of the circuit C is  $\geq \kappa \cdot (1+1/e)$ .

$<sup>^2 \</sup>verb|https://github.com/UzL-ITS/white-box-masking|$

To estimate the maximum bias  $\epsilon$  we use two auxiliary notions: algebraic encoding security which addresses the security of the encoding function E and algebraic circuit security which addresses the security of any Boolean function C:

**Definition 6** (Algebraic Encoding Security  $(\epsilon\text{-1-AS})$ ). Let  $E(\overline{x}, \overline{r}) : \mathbb{F}_2^N \times \mathbb{F}_2^{R_E} \to \mathbb{F}_2^{N'}$  be an arbitrary encoding function. Let  $\mathcal{Y}$  be the set of functions given by the output bits of E. The function E is called 1<sup>st</sup>-order algebraically  $\epsilon$ -secure  $(\epsilon\text{-1-AS})$  if for any  $f \in \mathcal{Y}^{(1)} \setminus \{\mathbf{0}, \mathbf{1}\}$  and for any  $\overline{x} \in \mathbb{F}_2^N$  the bias of the function  $f(\overline{x}, \cdot) : \mathbb{F}_2^{R_E} \to \mathbb{F}_2$  is not greater than  $\epsilon$ :

$$\max_{f \in \mathcal{Y}^{(1)} \backslash \{\mathbf{0},\mathbf{1}\},\overline{x} \in \mathbb{F}_2^N} \mathcal{E}(f(\overline{x},\cdot)) \leq \epsilon$$

**Definition 7** (Algebraic Circuit Security  $(\epsilon\text{-1-AS})$ ). Let  $C(\overline{x}, \overline{r}) : \mathbb{F}_2^{N'} \times \mathbb{F}_2^{R_C} \to \mathbb{F}_2^M$  be a Boolean circuit and let  $\epsilon$  be a real number, with  $0 \le \epsilon < 1/2$ . Then C is called first-order algebraically  $\epsilon$ -secure  $(\epsilon\text{-1-AS})$  if for any  $f \in \mathcal{F}^{(1)}(C) \setminus \{\mathbf{0}, \mathbf{1}\}$  one of the following conditions holds:

- (a) f is an affine function of  $\overline{x}$ ,

- (b) for any  $\overline{x} \in \mathbb{F}_2^N$ ,  $\mathcal{E}(f(\overline{x},\cdot)) \leq \epsilon$  where  $f(\overline{x},\cdot) : \mathbb{F}_2^{R_C} \to \mathbb{F}_2$ .

In the rest of this section we show that our basic gadgets are  $\epsilon$ -1-AS, for some  $\epsilon < 1/2$  (Sec. 4.3.1). Using the fact that composition of two  $\epsilon$ -1-AS circuits remains  $\epsilon$ -1-AS [BU18] we get that the whole circuit C is  $\epsilon$ -1-AS. In Section 4.3.2 we show that our encoding function E is  $\epsilon$ -1-AS, for some  $\epsilon < 1/2$ , and finally we conclude that  $\max_{f_{\pi} \in \mathcal{R}_d} \mathcal{E}(f_{\overline{x}}) \leq \epsilon$ .

### 4.3.1 $\epsilon$ -1-AS of the Gadgets

Using the above definitions, we employ the following methodology to prove the 1-PS of our scheme. We first divide the circuit into smaller circuits (namely And, Xor and RefreshMask gadgets as defined in Section 3.1) and show that the gadgets satisfy Definition 6. This gives us a bias bound for the individual gadgets. Using the 1-AS composability result in [BU18] we make sure that any composition of our gadgets (C) is also 1-AS. Finally, we combine C with the encoding function E and complete the 1-PS security proof of our scheme by using Proposition 1 .

While proving algebraic encoding security is quite straightforward, proving algebraic circuit security needs significant attention. The methodology to prove algebraic circuit security in [BU18] can be divided into two steps. The first step consists of showing  $\mathcal{E}(f(\overline{x},\overline{r})) \neq 1/2$  for all  $f \in \mathcal{F}^{(1)}(C)$  and for all  $\overline{x} \in \mathbb{F}_2^N$  except for constant functions and affine functions of  $\overline{x}$ . A verification algorithm is provided in [BU18]. The algorithm generates a truth table by evaluating the circuit on all possible inputs and records each node in the circuit. Another truth table is formed by selecting the values where the input is fixed  $\overline{x} = \overline{c}$ . That is, the second truth table corresponds to the values of the circuit nodes where the input  $\overline{x}$  is fixed to a value  $\overline{c}$  while  $\overline{r}$  takes all possible values. Observe that the latter truth table is a subset of the former one. Finally, the algorithm compares the dimensions of the basis of the truth tables for each restriction, to check if there is a constant function f when the input is fixed to a value  $\overline{c}$ .

The second step is to find the maximum degree term (i.e. node in the circuit) and calculate the corresponding bias bound. As proven in [MS77], the degree of any nonzero Boolean function  $g: \mathbb{F}_2^N \to \mathbb{F}_2$  gives us the following lower bound for the weight of the function:  $wt(g) \geq 2^{N-\deg(g)}$ , where N is the number of inputs of the function g. Symmetrically<sup>3</sup>, we get that for any function  $g \neq 1$  it is true that  $wt(g) \leq 2^N - 2^{N-\deg(g)}$ .

General and a substantial of a substantial and substa

Thus, for any non-constant function g we have:

$$2^{N-\deg(g)} \le wt(g) \le 2^N - 2^{N-\deg(g)}$$

.

Using these inequalities we can analyze the bias bound of any non-constant function  $f \in \mathcal{F}^{(1)}(C)$  as follows. First, we bound  $\epsilon$  as:

$$\epsilon = \left| \frac{1}{2} - \frac{wt(f)}{2^N} \right| \le \frac{1}{2} - \frac{2^{N - \deg(f)}}{2^N} = \frac{1}{2} - \frac{1}{2^{\deg(f)}}.$$

(4)

Next, observe that the maximum degree of f is equal to the maximum degree node in C, since f contains *only* linear combinations of the nodes. That is, for all  $f \in \mathcal{F}^{(1)}(C)$ ,  $\deg(f) \leq \max(\deg(c_i)_{c_i \in C})$ . Thus, the linear-bias bound of the gadget can be estimated as:

$$\epsilon \leq \frac{1}{2} - 1/2^{\max(\deg(c_i)_{c_i \in C})}.$$

Due to the first part of the proof, we know that there are no constant functions and therefore the bias cannot grow. Using the discussion above, we will prove the security of our gadgets by showing that there exists no constant function  $f(\overline{x},\cdot) \in \mathcal{F}^{(1)}(C)$  for all  $\overline{x} \in \mathbb{F}_2^N$  and by calculating the corresponding bias bound of the gadgets. We start with the first-order algebraic security proof for a RefreshMask[n,1] gadget that uses the construction given in Section 3.1.

**Proposition 5.** Let  $C(\overline{x},\overline{r}):\mathbb{F}_2^{n+2}\times\mathbb{F}_2^{R_C}\to\mathbb{F}_2^{n+2}$  be the circuit representation of the RefreshMask gadget using a masking scheme with an arbitrary order n and a fixed degree d=1. C takes as input n+2 shares  $(\tilde{x}_0,\tilde{x}_1,(x_i)_{1\leq i\leq n})$  and outputs n+2 shares  $(\tilde{x}_0,\tilde{x}_1,(x_i)_{1\leq i\leq n})$ . The gadget RefreshMask[n,1] is  $\epsilon$ -1-AS with  $\epsilon:=1/4$ .

*Proof.* In the first part of the proof, we show that, except of affine functions of inputs, there exists no function  $f \in \mathcal{F}^{(1)}(C) \setminus \{\mathbf{0}, \mathbf{1}\}$  such that f is constant when inputs are fixed. Assume  $(\tilde{x}_0, \tilde{x}_1, (x_i)_{1 \leq i \leq n})$  are some fixed but arbitrary inputs and let  $f \in \mathcal{F}^{(1)}(C) \setminus \{\mathbf{0}, \mathbf{1}\}$  be a function of random bits for the fixed input. As seen in Algorithm 3, all nodes used in RefreshMask gadget, behind the nodes for computing the values  $\mathcal{W}$  and  $\mathcal{R}$  in line 11, are xor-gates. Thus, if f involves only those nodes it is either an affine function of inputs or it is non-constant.

Next, by the definition of W each input bit  $\tilde{x}_0$  and  $\tilde{x}_1$  in W is accompanied additively by a random value. And  $\mathcal{R}$  contains only random values. To compute the expressions, behind xor-gates, there are used three and-gates which output the values:

- $\tilde{r}_0\tilde{x}_1 \oplus \tilde{r}_0r_0$

- $\tilde{r}_1\tilde{x}_0 \oplus \tilde{r}_1r_0$ , resp.

- $\tilde{r}_0\tilde{r}_1 \oplus \tilde{r}_0r_0 \oplus r_0\tilde{r}_1 \oplus r_0\tilde{r}_0$ .

Thus, the only way to obtain a constant function f which involves the nodes used to compute the expression in line 11, is to xor the first or the second value above with  $\tilde{r}_0 r_0$ , resp. with  $\tilde{r}_1 r_0$ . But, as one can easily check, no node used in Algorithm 3, computes the corresponding values. Hence we can conclude that there exists no constant function  $f \in \mathcal{F}^{(1)}(C)$  such that inputs are fixed expect of affine functions of inputs.

In the second part, we examine the highest degree term in the gadget. The maximum degree term can be found in  $\mathcal{R}$  with degree 2. Therefore the corresponding bias and the bias bound of the gadget can be calculated as  $\epsilon \leq 1/2-1/2^2=1/4$ . Thus the RefreshMask gadget is  $\epsilon$ -1-AS with  $\epsilon := 1/4$ .

**Table 3:** First-order algebraic security verification of individual gadgets. Input corresponds to the number of shares for both inputs (i.e. 2(n+2)). Random states the number of random values  $(R_C)$  within the circuit and it is calculated by the randomness requirement of two RefreshMask gadgets and additional randomness in the gadget. The number of intermediate variables represents the number of nodes in the gadget.

|                     | 3.6 1      | D: D 1     | т ,   | D 1    | T , 1: ,     | m·                         |

|---------------------|------------|------------|-------|--------|--------------|----------------------------|

|                     | Max degree | Bias Bound | Input | Random | Intermediate | Time                       |

| $\mathtt{Xor}[1,1]$ | 2          | 1/4        | 6     | 6      | 8            | $3.5\mathrm{s}$            |