# Compress: Generate Small and Fast Masked Pipelined Circuits

Gaëtan Cassiers<sup>1\*</sup>, Barbara Gigerl<sup>2</sup>, Stefan Mangard<sup>2</sup>, Charles Momin<sup>1</sup> and Rishub Nagpal<sup>2,3</sup>

<sup>1</sup> UCLouvain, Louvain-la-Neuve, Belgium, firstname.lastname@uclouvain.be

<sup>2</sup> Graz University of Technology, Graz, Austria, firstname.lastname@iaik.tugraz.at

<sup>3</sup> Silicon Austria Labs, TU-Graz SAL DES Lab, Graz, Austria

Abstract. Masking is an effective countermeasure against side-channel attacks. It replaces every logic gate in a computation by a gadget that performs the operation over secret sharings of the circuit's variables. When masking is implemented in hardware, care should be taken to protect against leakage from glitches, which could otherwise undermine the security of masking. This is generally done by adding registers, which stop the propagation of glitches, but introduce additional latency and area cost. In masked pipeline circuits, a high latency further increases the area overheads of masking, due to the need for additional registers that synchronize signals between pipeline stages. In this work, we propose a technique to minimize the number of such pipeline registers, which relies on optimizing the scheduling of the computations across the pipeline stages. We release an implementation of this technique as an open-source tool, COMPRESS. Further, we introduce other optimizations to deduplicate logic between gadgets, perform an optimal selection of masked gadgets, and introduce new gadgets with smaller area. Overall, our optimizations lead to circuits that improve the state-of-the art in area and achieve state-of-the-art latency. For example, a masked AES based on an S-box generated by COMPRESS reduces latency by 19% and area by 27% over a state-of-the-art implementation, or, for the same latency, reduces area by 45 %.

Keywords: Side-channel  $\cdot$  Masking  $\cdot$  HPC

## 1 Introduction

Physical side-channel attacks that exploit information leakage such as the power consumption or the electromagnetic radiation of cryptographic implementations are an important security threat. Masking is a common countermeasure against these attacks [CJRR99]. Its core principle is to replace every variable x in a computation with a secret sharing  $\boldsymbol{x} = (x_0, \ldots, x_{d-1})$  such that  $x = x_0 \star \cdots \star x_{d-1}$ , where  $\star$  is a group law over any set of d-1 shares  $x_i$ . A common example is Boolean masking, where variables belong to  $\mathbb{F}_2$ and the group operation is the exclusive or  $(\oplus)$ . The computations to mask are typically decomposed in elementary operations (e.g., simple logic gates) which are then replaced by gadgets: small circuits that securely perform computations over shared data.

Masking a circuit in a secure way is a challenging task. Physical defaults such as glitches and transitions can break the independence assumptions required for a secure masked implementation [MPG05, NRS11]. Furthermore, the security of small gadgets may not directly extend to their combination, leading to so-called composition issues [CPRR13, BBD<sup>+</sup>16]. Physical defaults and composition issues can also arise in a

<sup>\*</sup> Work performed in part while associated with Graz University of Technology, Graz, Austria.

combined way [FGP<sup>+</sup>18, MMSS19, MKSM22]. One possible solution to these challenges is using the hardware private circuits (HPC) masking scheme [CGLS21, CS21], which is composable even in the presence of glitches and transitions. With the HPC scheme, linear and affine operations can be implemented by simple sharewise gadgets, while non-linear gadgets are more complex. Several multiplication (or AND) gadgets have been proposed, including the two-cycle HPC1 and HPC2 [CGLS21], and the single-cycle HPC3 [KM22].

Even though trivially composable masking schemes such as HPC simplify the security analysis of a masked circuit, transforming an unprotected design into a securely masked one remains a challenging task. Indeed, the HPC multiplication gadgets contain sequential logic, hence masking a non-linear combinational circuit leads to a sequential circuit, requiring adjustments to the synchronization logic to take the added latency into account. AGEMA [KMMS22] is an automated masked circuit generation tool that addresses this problem. However, the generated designs are often suboptimal, as pointed out by Momin et al. [MCS22], who introduce handcrafted designs for a masked AES implementation that have better performance than the circuits generated by AGEMA. While their performance gains come from carefully crafted high-level architectures and from an improved Sbox design. The latter is automatically generated by a tool that achieves better performances than AGEMA, but is much more restricted since it only handles pipelined circuits. This tool, as well as the recently-introduced AGMNC [WFP<sup>+</sup>23] (another tool that generates masked pipelined circuits), do not generate optimal circuits.

Although existing CAD tools implement advanced circuit optimizations, using them to optimize masked designs is non-trivial, since they do not necessarily preserve the required security properties. For example, arbitrary re-timing of registers might allow the propagation of insecure glitches, and logic sharing, along with boundary optimizations may break Threshold Implementation's [NRR06] non-completeness property [CBG<sup>+</sup>17, ABP<sup>+</sup>18, ZSS<sup>+</sup>21, CCGB21, MM22, CMM<sup>+</sup>23b]. In practice, designers therefore generally take measures to disable or prevent critical CAD tools' optimizations when synthesizing masked circuits.

**Contributions** In this work, we introduce COMPRESS<sup>1</sup>, a tool to generate area-optimized masked pipelined circuits. We make COMPRESS publicly available on Github<sup>2</sup>. COMPRESS takes as an input a Boolean circuit describing the circuit to be implemented, and generates a masked netlist representing the circuit with a latency chosen by the user. Thanks to its optimizations, it generates more efficient circuits than state-of-the-art tools, while keeping security-critical structures for masking. The tool supports any-order Boolean masking, although the techniques it uses also apply to other kinds of masking.

We focus on the generation of pipelined circuits, i.e., circuits that are composed of a sequence of combinational logic stages, where the wires that connect a stage to the next are going through registers (typically implemented as D-flip-flops). We build these circuits by composing HPC gadgets (which are themselves small pipelined circuits) together with the help of additional registers to ensure proper synchronization of the pipeline stages. Compared to the alternatives such as clock gating [KMMS22], the big advantage of pipelined circuits is their simplicity (e.g., there is no control logic) and high throughput (they perform one evaluation per clock cycle). This makes them good candidates for the implementation of subcomponents in cryptographic algorithms, where the high throughput enables serialized implementation strategies, and a single pipelined circuit is used to perform many parallel computations sequentially (e.g. S-boxes). Pipelined circuits can then be integrated in circuits with more complex architectures, either by hand [MCS22], or automatically (e.g., with EASIMASK [BSG23]).

<sup>&</sup>lt;sup>1</sup>Composable Optimizer of Masked Pipelines with Register-Enhanced Staging Selection

<sup>&</sup>lt;sup>2</sup>Available at https://github.com/cassiersg/compress, with all our scripts at https://github.com/cassiersg/compress\_artifact.

While most previous works focus rather on finding efficient Boolean circuit representations of functions [BP12, CGLS21] or designing new gadgets with reduced randomness usage or lower latency, these works generally leave out "low-hanging fruit" optimizations in the composition of gadgets and inside the gadgets themselves. Most of our optimizations therefore focus on eliminating and re-timing registers in masked pipelines, which sometimes represent more than 70 % of the area [MCS22]. This is achieved in two steps. First, at the gadget composition level, we optimize the staging of computations, i.e., we assign every gadget in the composition to its pipeline stage(s). If needed, we duplicate gadgets, for example, when a gadget is small and its output is used in multiple pipeline stages, it might be more efficient to instantiate the gadget multiple times, instead of having pipeline registers to forward its output to all later pipeline stages where it is used. Second, we tackle the issue of redundant pipeline registers, that is, multiple registers that store the same value. This issue arises when gadgets store their inputs in registers, which may be redundant with pipeline registers inside other gadgets, or registers added for synchronization between gadgets.

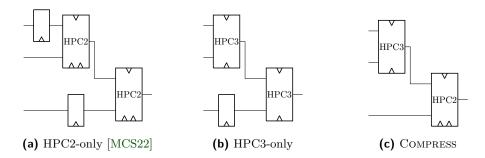

Furthermore, COMPRESS introduces a variety of other optimizations to reduce the area of masked designs. At the level of individual HPC2 and HPC3 gadgets, we employ an optimized handling of the so-called *inner-domain* terms (i.e., term of the form  $x_i \wedge y_i$ , for input sharings  $\boldsymbol{x} = (x_0, \ldots, x_{d-1})$  and  $\boldsymbol{y} = (y_0, \ldots, y_{d-1})$ ). This optimization also leads to new variants of HPC2 and HPC3 that implement the Toffoli gate in a more efficient way than the AND-XOR gadgets of [WFP<sup>+</sup>23], and to the extension of HPC3 to arbitrary fields, enabling its use in more contexts (such as efficient implementations of the Canright AES Sbox [Can05]). Finally, we show for the first time that saving area is possible through combining HPC2 and HPC3 gadgets, rather than exclusively using one or the other. In general, HPC3 has a lower latency and lower area than HPC2, but it requires double the amount of randomness, leading to a larger total area (i.e., including the area of the randomness generation circuit). Small and low-latency circuits can be obtained by sticking to HPC3 when the operands are both on the critical latency path, but HPC2 elsewhere (thanks to its 1-2 cycle asymmetric latency).

Combining all these optimizations leads to significant area reductions, and makes low-latency circuits (which are generally larger) more practically-relevant. In particular, we design a pipelined AES S-box with up to 50 % latency and 33 % area gain over the smallest HPC2 implementation in the state of the art, and 45 % area gain over the state of the art HPC3 implementation (same latency). We further adapt the 32-bit datapath state-of-the-art masked AES HPC implementation of [MCS22], leading to an overall latency and throughput improvement of 19 %, and an area reduction of 27 %. Our round-based AES implementations also exhibit similar improvements over the state of the art in area and/or latency. COMPRESS is not limited to the design of masked S-boxes. As an example, we apply it to multiple architectures of 32-bit adders.

**Outline** Section 2 introduces the HPC masking scheme and its use to build pipelined circuits from gadgets. Section 3 presents the core ideas behind COMPRESS and the optimization problem it solves. Section 4 discusses the optimizations to deduplicate pipelining registers inside gadgets, and Section 5 details the other optimizations to the HPC2 and HPC3 gadgets. Next, Section 6 discusses the results of the tool and compares it to the state of the art for multiple masked circuits: AES S-box and its integration in a complete masked AES, Skinny S-box and binary adders. Finally, we discuss in more detail the related works (Section 7).

Algorithm 1 Sharewise-X with d shares.

Input: Sharings  $\boldsymbol{x}, \boldsymbol{y}$ , binary gate X (e.g., XOR, AND...). Output: Sharing  $\boldsymbol{z}$ . for i = 0 to d - 1 do

$z_i = \mathsf{X}\left(x_i, y_i\right)$

Algorithm 2 HPC2 AND gadget with d

Algorithm 3 HPC3 AND gadget with d

shares.

shares.

| <b>Input:</b> Sharings $x$ , $y$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>Input:</b> Sharings $x$ , $y$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Output:</b> Sharing $z$ such that $z = x \land y$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Output:</b> Sharing $z$ such that $z = x \land y$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $\begin{aligned} & \mathbf{for} \ i = 0 \ \mathrm{to} \ d - 1 \ \mathbf{do} \\ & \mathbf{for} \ j = i + 1 \ \mathrm{to} \ d - 1 \ \mathbf{do} \\ & r_{ij} \stackrel{\$}{\leftarrow} \mathbb{F}_2; \ r_{ji} \leftarrow r_{ij} \\ & \mathbf{for} \ i = 0 \ \mathrm{to} \ d - 1 \ \mathbf{do} \\ & p_{ii} \leftarrow PR(x_i PR(y_i)) \\ & \mathbf{for} \ j = 0 \ \mathrm{to} \ d - 1, j \neq i \ \mathbf{do} \\ & p_{ij} \leftarrow R(\overline{x_i} \land PR(r_{ij})) \oplus R(x_i \land R(y_j \oplus r_{ij})) \\ & z_i \leftarrow \bigoplus_{j=0}^{d-1} p_{ij} \end{aligned}$ | $ \begin{aligned} & \textbf{for } i = 0 \text{ to } d - 1 \textbf{ do} \\ & \textbf{for } j = i + 1 \text{ to } d - 1 \textbf{ do} \\ & r_{ij} \stackrel{\$}{\leftarrow} \mathbb{F}_2; \ r_{ji} \leftarrow r_{ij} \\ & r'_{ij} \stackrel{\$}{\leftarrow} \mathbb{F}_2; \ r'_{ji} \leftarrow r'_{ij} \\ & \textbf{for } i = 0 \text{ to } d - 1 \textbf{ do} \\ & p_{ii} \leftarrow PR(x_i \land y_i) \\ & \textbf{for } j = 0 \text{ to } d - 1, j \neq i \textbf{ do} \\ & p_{ij} \leftarrow R\left((\overline{x_i} \land r_{ij}) \oplus r'_{ij}\right) \oplus PR(x_i) \land R(y_j \oplus r_{ij}) \\ & z_i \leftarrow \bigoplus_{j=0}^{d-1} p_{ij} \end{aligned} $ |

## 2 Background

In this section, we first introduce the glitch- and transition-robust probing model for analyzing the security of masking schemes in hardware. We then present the HPC masking schemes and its various multiplication gadgets. Finally, we discuss the issue of synchronization in masked circuits.

### 2.1 Robust Probing Model

The security of masked circuits is often evaluated in the *t*-probing model [ISW03], where computations are represented as an abstract arithmetic circuit, and the adversary may probe the values carried by any set of *t* wires in the circuit (*t* is known as the masking order). A circuit is secure if the values observed by the adversary are independent of the sensitive values, i.e., all non-masked values represented by sharings in the circuit. When masking with *d* shares, the security order *t* is at most d - 1.

When considering glitches and transitions, the circuit model is closer to concrete synchronous circuits, where the computation is executed over multiple clock cycles, and registers carry values from one clock cycle to the next [CS21]. For these circuits, the robust probing model [FGP<sup>+</sup>18] allows the adversary to use extended probes, which leak the value of multiple wires. For a glitch-extended probe, the observed wires are all the wires that belong to the combinatorial circuit that computes the probed wire, i.e., glitches propagate through combinatorial gates but are stopped by registers. For a transition-extended probe, the value carried by the probed wire is observed at two consecutive clock cycles. A glitch+transition-extended probe represents the combination of these models, giving access to all wires in the combinatorial circuit for two consecutive clock cycles.

### 2.2 Hardware Private Circuit

HPC is an arbitrary-order masking scheme with t = d - 1 robust probing security against glitches and transitions [CGLS21, CS21]. To mask a circuit with HPC, it must be decomposed in simple gates (typically XOR, AND, NOT). Then, conceptually, each wire is replaced by a sharing and each gate is replaced by a gadget. HPC is based on the

| Gadget                                | Latency<br>ina | Latency<br>inb | d                  | Random<br>bits                                                                     | Area w/o PRNG<br>(GE)                                                               | Area w/ PRNG<br>(GE)                | Group          |

|---------------------------------------|----------------|----------------|--------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------|----------------|

| GHPC [KSM22]                          | 1              | 2              | <b>2</b>           | 1                                                                                  | 95.3                                                                                | 134.7                               | $\mathbb{F}_2$ |

| $\mathrm{GHPC}_{\mathrm{LL}}$ [KSM22] | 1              | 1              | <b>2</b>           | 4                                                                                  | 86.7                                                                                | 244.1                               | $\mathbb{F}_2$ |

| HPC1 [CGLS21]                         | 1              | 2              | $2 \\ 3 \\ 4 \\ 5$ | $2 \\ 5 \\ 10 \\ 15$                                                               | 50.7<br>127.0<br>217.3<br>325.0                                                     | $129.4 \\ 323.8 \\ 610.9 \\ 915.4$  | $\mathbb{F}_n$ |

| HPC2 [CGLS21]                         | 1              | 2              | $2 \\ 3 \\ 4 \\ 5$ | $     \begin{array}{c}       1 \\       3 \\       6 \\       10     \end{array} $ | 82.3<br>209.0<br>392.7<br>633.3                                                     | $121.7 \\ 327.1 \\ 628.8 \\ 1026.9$ | $\mathbb{F}_2$ |

| HPC2o (new)                           | 1              | 2              | $2 \\ 3 \\ 4 \\ 5$ | $     \begin{array}{c}       1 \\       3 \\       6 \\       10     \end{array} $ | 55.0<br>168.3<br>338.7<br>566.0                                                     | $94.4 \\286.4 \\574.8 \\959.6$      | $\mathbb{F}_2$ |

| HPC3 [KM22]                           | 1              | 1              | $2 \\ 3 \\ 4 \\ 5$ | $2 \\ 6 \\ 12 \\ 20$                                                               | $ \begin{array}{r}     69.3 \\     165.0 \\     301.3 \\     478.3 \\ \end{array} $ | $148.1 \\ 401.2 \\ 773.7 \\ 1265.5$ | $\mathbb{F}_2$ |

| HPC3o (new)                           | 1              | 1              | $2 \\ 3 \\ 4 \\ 5$ | $2 \\ 6 \\ 12 \\ 20$                                                               | $38.7 \\119.0 \\240.0 \\401.7$                                                      | $117.4 \\ 355.2 \\ 712.3 \\ 1188.9$ | $\mathbb{F}_n$ |

**Table 1:** Performance characteristics of multiplication/AND gadgets (randomness and area given for  $\mathbb{F}_2$  with the NanGate45 PDK).

composable notion of glitch-robust probe-isolating non-interference (PINI) [CS20], which ensures that gadgets are trivially composable in the presence of glitches: if all gadgets are glitch-robust PINI, the masked circuit is glitch-robust PINI as well. Further, HPC has also been proven secure against glitch+transition leakage under some additional conditions on its structure, which are trivially satisfied in many cases, such as when implementing a substitution-permutation network (SPN) with at least 2 clock cycles per round [CS21].

For linear gates (e.g., XOR), there exists simple sharewise gadgets (e.g., Sharewise-XOR shown in Algorithm 1) which are glitch-robust PINI. Similarly, for affine gates, we can use a sharewise gadget where the affine map is applied to one of the shares and the associated linear map is applied to the other shares (e.g., a NOT gadget may simply apply the NOT on the first share). Non-linear gates are more complex, and the design of multiplication/AND gadgets is an active research area, with state-of-the-art gadgets listed in Table 1. The gadgets are characterized by their latency (number of cycles between providing each of the input sharings and generating the output), the number of shares supported, their randomness usage and area requirement.

Given the high randomness requirements of the HPC gadgets, masked circuits using them generally use dedicated PRNGs. Assuming that such a PRNG is used allows us to simplify the gadget comparison: we estimate the area of the PRNG needed to provide enough randomness to run the gadget continuously, and integrate it in the area of the gadget. We therefore compare gadgets based on their area with randomness generation, and do not focus on the randomness usage itself. For the PRNG area of generating one bit of randomness per cycle, we take the area of an unrolled Trivium (as suggested by [CMM<sup>+</sup>23a]) divided by the unrolling factor (we take an unrolling factor of 512), amounting to 39.4 GE/bit with NanGate45.

In Table 1, it appears that HPC2 [CGLS21] and HPC3 [KM22] have respectively lower (PRNG-included) area than the Generic Hardware Private Circuit (GHPC) and its low latency variant (GHPC<sub>LL</sub>) [KSM22], for the same latency. HPC1 is similarly less performant than HPC2. We therefore mainly focus on the HPC2 and HPC3 gadgets in

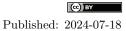

**Figure 1:** Example of a masked pipelined circuit as a composition of gadgets and masked registers.

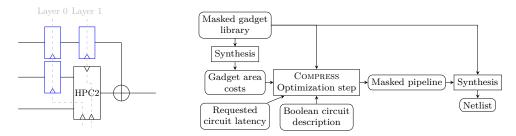

**Figure 2:** COMPRESS flow. Rectangles denote flow steps, rounded corners denote inputs, outputs and intermediate flow artifacts.

this paper, and use HPC1 only when multiplication in a larger field (i.e., not  $\mathbb{F}_2$ ) is used. The HPC2 and HPC3 gadgets are described in Algorithm 2 and Algorithm 3, where  $\mathsf{R}(\cdot)$  denotes a glitch-stopping register (i.e., one that is needed for security) and  $\mathsf{PR}(\cdot)$  denotes a pipeline register (i.e., one that is only needed for turning the gadget into a pipeline).

#### 2.3 Synchronization in Masked Hardware Circuits

While masking a circuit with only sharewise gadgets is a simple transformation, using the HPC2 or HPC3 gadget (or, generally, gadgets implementing a non-linear gate) is more complex because these gadgets introduce additional latency in the circuit. This means that masked non-linear sub-circuits such as S-boxes in SPNs often have a high latency, which may greatly diminish the overall efficiency of masked implementations [KMMS22]. Indeed, masking a circuit by simply replacing gates with gadgets will need to cleverly use clock gating to properly synchronize all the signals in the circuit, and pay a high cost in latency, on top of the area overhead of masking. Another strategy for masked implementations is to exploit pipelining: the synchronization is achieved through the addition of registers instead of clock gating, as shown in Figure 1. Pipelining does not improve latency and increases area cost, but it increases the throughput of the sub-circuit.

When multiple computations can be performed in parallel (e.g., a block cipher in a parallelizable mode of operation), pipelining translates into a large throughput gain over clock gating, at a small area overhead. Another way to exploit pipelining is to switch to a more serialized architecture. For example, in a round-based (parallel) implementation of an SPN, the masked S-box can be instantiated multiple times such that that all S-boxes can be evaluated in parallel (each instance is evaluated only once per round). By contrast, a serialized implementation may instantiate the masked S-box only once (or a few times) and evaluate it multiple times in order to evaluate a round. Serializing the architecture reduces the area cost, and it combines well with pipelining: the high throughput of the pipeline minimizes the latency overhead of serialization. As a result, masking with pipelining is a technique that can achieve better latency/area trade-offs than clock gating, but may require handcrafted designs [MCS22].

## 3 Generic Optimization of Masked Pipelined Circuits

COMPRESS takes as input the Boolean circuit to mask and outputs a netlist that implements the circuit as a masked HPC pipeline. As shown in Figure 2, COMPRESS also takes as input a masked gadget library, whose areas (including PRNG cost) are used to parameterize an optimization goal. The latency of the generated circuit is also a parameter of COMPRESS,

**Figure 3:** AND3 implementation with minimal latency: COMPRESS reaches the minimum possible latency, while combining HPC2 and HPC3 gadgets to minimize the total area.

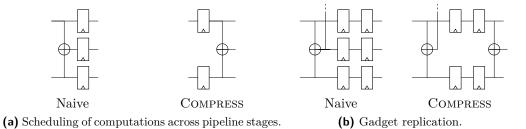

**Figure 4:** Examples of COMPRESS optimization of pipeline registers (registers and  $\oplus$  represent sharewise gadgets, wires represent sharings).

it must be at least equal to the AND depth of the input circuit (otherwise the circuit cannot be implemented using the HPC2 and HPC3 gadgets).

The goal of COMPRESS is to generate a pipeline of masked gadgets with optimal gadget selection and computation scheduling in order to achieve the requested latency while minimizing area. The tool exploits the following degrees of freedom: gadget selection, scheduling of computations across pipeline stages, and gadget replication. First, COMPRESS selects a suitable gadget for AND gates. There are multiple gadgets with different latency, area and randomness usage characteristics (HPC2, HPC3, etc.) available, as illustrated in Figure 3. The assignment of input sharings is also considered in case of asymmetric gadgets, such as HPC2. Second, COMPRESS optimizes the scheduling of computations by deciding which pipeline stage a computation should best be performed in, and instantiating the pipeline registers that forward the computed data across register stages. Optimized scheduling reduces the number of pipeline registers to be instantiated, thereby reducing area as shown in Figure 4a. Third, COMPRESS may perform gadget replication, which means that if a value is used in multiple clock cycles and the gadget that computes it is small (e.g., an XOR gadget), it might be more efficient to replicate the gadget in multiple pipeline stages instead of instantiating pipeline registers (provided that the operands of the gadget are available at the corresponding pipeline stages). For example, in Figure 4b, an XOR gadget is duplicated in order to avoid the instantiation of two masked registers (the dashed line indicates a value used elsewhere in the circuit).

The core part of COMPRESS consists representing the masked circuit generation as a constraint optimization problem. We then use OR-tools [PF] to solve this problem, and the solution is then translated into a verilog netlist. We next give a high-level description of this optimization problem (the complete algorithm is given in Appendix B).

COMPRESS splits the computation in pipeline stages  $0, \ldots, L$ , where the inputs are fed in the circuit at stage 0, while the outputs are connected to stage L. For each intermediate value w in the Boolean circuit and for each pipeline stage s, COMPRESS instantiates a "valid" Boolean variable  $v_s^w$ , which is true iff there is a sharing representing the value w in the pipeline stage s. For each of these variables, there is also a "compute" Boolean variable  $c_s^w$  that is true iff there is a gadget that outputs w at the stage s (for now, we consider gadgets that output a single sharing, multi-output gadgets are handled in Appendix B). The "pipeline" variable  $r_s^w$  indicates the presence of a pipeline register that forwards the value of w from stage s to stage s + 1, for all w and for  $s \in \{0, \ldots, L-1\}$ . These variables are connected by the following constraints, which define the "valid" variable as a function of "compute" and "pipeline":

$$\begin{aligned} v_0^w &= c_0^w \\ v_s^w &= c_s^w \vee \left( v_{s-1}^w \wedge r_{s-1}^w \right) \quad \text{for } s > 0. \end{aligned}$$

Let us next model the instantiation of gadgets, which will determine the value of the "compute" variables. Each value w is computed by a logic gate (e.g. XOR, AND, ...) that can be implemented by one or multiple gadget types (e.g., an XOR gate can only be implemented by an XOR gadget, while an AND gate can be implemented by HPC2 or HPC3). For each value w, each stage s, and each gadget type t the "gadget" Boolean variable  $g_s^{t,w}$  indicates if a gadget of type t is instantiated to output w in stage s. In order to ensure correctness of the generated circuit,  $g_s^{t,w}$  is set to false (i.e., the gadget is not instantiated) when (i) the gadget implements a different gate than the one computing w, or (ii) when the corresponding gadget would take an input before stage 0 (e.g., for any w,  $g_0^{\text{HPC2},w} = g_1^{\text{HPC2},w} = \bot$ , i.e., they are set to false). Next, the following constraint requires the inputs of an instantiated gadget to be valid: we let

$$g_s^{t,w} \Rightarrow \bigwedge_{w' \in \mathsf{op}(w)} v_{s-\mathsf{lat}(t,w,w')}^{w'},$$

where op(w) is the set of operands of the logic gate that computes w, while lat(t, w, w') is, for the gadget t, the latency of the input sharing w' relative to the output sharing w (i.e., the difference in pipeline stages between the input and the output).

Gadget instantiations determine the value of the "compute" variables:

$$c_s^w = \bigvee_{t \in G} g_s^{t,w}$$

where G is the set of all gadget types<sup>3</sup>. As an exception, the inputs of the circuit are not computed by gadgets, they are provided at stage 0, which we model as follows: for all input wires  $w, c_0^w = \top$  and  $c_s^w = \bot$  for all s > 0.

The last constraint is for outputs: for all output wires  $w, v_L^w = \top$ . Together, the constraints ensure that any admissible solution to the problem corresponds to a correct masked circuit implementation<sup>4</sup>.

Next, the objective of the optimization problem is the minimization of the area used by the masked circuit. Therefore, COMPRESS takes as an input the area cost of each gadget type, including a "pipeline register" gadget. The total cost is then defined as the sum of the areas of the instantiated gadgets (as determined by the  $g_s^{t,w}$  and  $r_s^w$  variables). We take into account the cost of randomness generation for the masked gadgets as follows. We assume that a PRNG is instantiated along with the masked circuit, and that it should provide enough randomness to run the pipeline continuously: each randomness input of a gadget

<sup>&</sup>lt;sup>3</sup>In order to provide most optimization opportunities (including the optimizations performed by [MCS22]) for gadgets that have functionally identical input sharings with different latencies (e.g., HPC2), we have multiple variants of these gadgets in G that are all equivalent, up to a re-ordering of functionally identical inputs.

$<sup>^{4}</sup>$ Except that it allows useless and nonsensical pipeline register instantiations, but these never occur in practice thanks to the optimization.

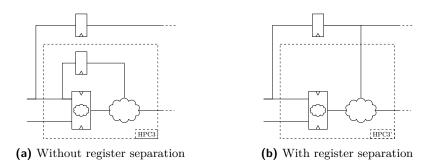

**Figure 5:** Illustration of register de-duplication thanks to the separation of a pipeline register out of the HPC3 gadget.

is connected to an output of the PRNG, and the PRNG should be able to refresh its full output at every clock cycle. Concretely, we use an unrolled Trivium, following [CMM<sup>+</sup>23a]. Then, we observe that the marginal area cost of one additional bit of randomness per clock cycle from the PRNG is roughly constant. As a result, the PRNG cost is included into the area optimization function as an increase of the area of each gadget by the area needed to generate the randomness it uses.

Let us finally remark that while the optimization problem is order-specific (the gadget costs depend on the masking order), COMPRESS's output is still generic: it can be synthesized at all masking order, provided that the gadgets support it.

## 4 Register Reuse through Gadget Decomposition

In this section, we further reduce the amount of registers in the masked circuits by looking at registers instantiated inside gadgets. For example, an HPC3 gadget contains pipeline registers for the  $x_i$  shares (see Algorithm 3). If two HPC3 gadgets have the same input sharing x, then these registers will be duplicated. The same can also happen between a register inside a gadget and a pipeline register outside any gadget. Our approach to avoid such inefficiencies is to decompose gadgets into multiple parts, which eliminates pipeline registers from such gadgets, and instead exposes them as latency constraints. This avoids duplication and COMPRESS's gadget selection (e.g., by choosing the order of the input sharings in a gadget) may bring further optimizations.

#### 4.1 Separate Pipeline Registers

As a first step, we handle the de-duplication of pipeline registers on input sharings, which is illustrated in Figure 5. The de-duplication is implemented in COMPRESS by putting these pipeline registers outside of the gadgets. If a gadget contains registers  $PR(x_i)$  (where  $\boldsymbol{x}$  is an input sharing, see e.g. HPC3), these can be removed from the gadget and these values replaced by the shares  $x'_i$  of a new input sharing. The new input sharing  $\boldsymbol{x'}$  is encoded as taking the same value of  $\boldsymbol{x}$ , but being used one clock cycle later than  $\boldsymbol{x}$ . This leads COMPRESS to instantiate a pipeline register to generate  $\boldsymbol{x'}$ , which may be used as an input for other gadgets. Concretely, this technique is applied to the input shares  $y_i$  of HPC2 (separating d registers), and to the input shares  $x_i$  and  $y_i$  of HPC3 (separating 2dregisters).

The new gadgets bring new additional constraints in COMPRESS. Indeed, a naive implementation of the techniques presented above would require that the values represented by the sharings x and x' are the same, while, for the circuit to be correct, the values of the individual shares must be equal. These conditions are not equivalent due to the

$\frac{ \textbf{Algorithm 4 HPC3-cross gadget with } d \text{ shares.}}{\textbf{Input: Sharings } \boldsymbol{x}, \boldsymbol{y}.}$

| Output: SI                         | naring $\boldsymbol{z}$ .                                                                                                                                   |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| for $i = 0$                        | to $d-1$ do                                                                                                                                                 |

| for $j =$                          | i+1 to $d-1$ do                                                                                                                                             |

| $r_{ij} \stackrel{\$}{\leftarrow}$ | $\mathbb{F}_2; r_{ji} \leftarrow r_{ij}$                                                                                                                    |

| $r'_{ij} \xleftarrow{\$}$          | $\mathbb{F}_2; \ r'_{ji} \leftarrow r'_{ij}$                                                                                                                |

| for $i = 0$                        | to $d-1$ do                                                                                                                                                 |

|                                    | 0 to $d-1, j \neq i$ <b>do</b>                                                                                                                              |

| $p_{ij} \leftarrow$                | $R\left(\left(\overline{x_{i}} \land PR\left(r_{ij}\right)\right) \oplus r'_{ij}\right) \oplus R\left(x_{i} \land R\left(y_{j} \oplus r_{ij}\right)\right)$ |

| $z_i \leftarrow \bigoplus$         | $igg _{j=0,j eq i}^{d-1} p_{ij}$                                                                                                                            |

# Algorithm 5 HPC3 AND decomposed in gadgets.

0----0----

**Input:** Sharings  $\boldsymbol{x}, \boldsymbol{y}$ **Output:** Sharing  $\boldsymbol{z}$  such that  $z = x \cdot y$ .

$oldsymbol{a} \leftarrow \mathsf{HPC3} ext{-cross}\left(oldsymbol{x},oldsymbol{y}

ight) \ oldsymbol{b} \leftarrow \mathsf{Sharewise} ext{-AND}\left(oldsymbol{x},oldsymbol{y}

ight)$

$oldsymbol{z} \leftarrow \mathsf{Sharewise}\mathsf{-XOR}\left(oldsymbol{a},oldsymbol{b}

ight)$

duplication of gadgets discussed in Section 3, when a non-deterministic gadget (i.e., one whose output sharing depends on some randomness) gets duplicated<sup>5</sup>. To ensure that such a case does not happen, we add constraints to the optimization problem of COMPRESS, enforcing all sharings of the same value to be identical<sup>6</sup>. Concretely, this means that a sharing cannot be computed by gadgets of different types: for all wires w,

$$\mathsf{AtMostOne}\left(\left(\mathsf{Any}\left(\left(g_{s}^{t,w}\right)_{s=0,\ldots,L}\right)\right)_{t\in G}\right) = \top,\tag{1}$$

where  $Any(\cdot)$  is true if any element of its input tuple is true, and  $AtMostOne(\cdot)$  is true if at most one element of its input tuple is true. Further, a gadget that uses randomness cannot be duplicated: for all wires w and all gadget types t that use randomness,

$$\mathsf{AtMostOne}\left(\left(g_s^{t,w}\right)_{s=0,\ldots,L}\right) = \top.$$

(2)

Regarding security, the only change we apply to the circuit is the de-duplication of registers that store identical values, which does not change the set of probes in the probing model (including glitches and transitions).

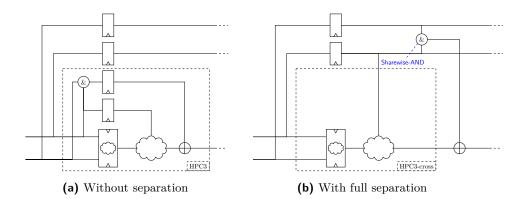

#### 4.2 Separate Inner-domain Terms

While some pipeline registers can be optimized by separating them out of the gadgets, the above optimization does not apply to all pipeline registers. In this section, we look at the pipeline registers on the so-called *inner-domain* terms in the HPC2 and HPC3 gadgets, namely the terms  $x_i \wedge y_i$ . Indeed, since these terms perform only sharewise computation, registers are not needed for security, only for proper pipeline staging. Again, our goal is to move these registers outside of the gadgets, such the COMPRESS can optimize them.

We achieve this by splitting the AND gadgets into a part that computes the innerdomain terms (a sharewise AND gadget), a part that computes the other terms (HPC2/3cross), and a gadget that XORs their outputs (sharewise), as illustrated in Figure 6. The decomposition of HPC3 is given in Algorithm 4 and Algorithm 5, and the decomposition of HPC2 follows the same pattern. The three resulting gadgets perform exactly the same computation as the original gadget, except for the now-unspecified pipeline registers.

$<sup>^{5}</sup>$ The issue can also appear if a logic gate can be implemented by multiple types of gadgets (with or without randomness), and the "duplication" instantiates two different types.

<sup>&</sup>lt;sup>6</sup>These constraints are stronger than strictly necessary since we could apply them (recursively) only to inputs of gadgets with pipeline register separation. This is not an issue in practice, since the only logic gate for which we have multiple gadget types is the AND gate, and these gadgets (which are also the only ones using randomness) have a large area. Therefore, it is unlikely that duplicating these gadgets is more efficient than adding pipeline registers.

**Figure 6:** Illustration of register de-duplication thanks to register separation and innerdomain terms separation.

| shares.shares.Input: Sharing $\boldsymbol{x}$ w, $\boldsymbol{x}$ , $\boldsymbol{y}$ .Input: Sharing $\boldsymbol{x}$ such that $z = w \oplus (x \land y)$ .for $i = 0$ to $d - 1$ dofor $i = 0$ to $d - 1$ dofor $i = 0$ to $d - 1$ dofor $i = 0$ to $d - 1$ do $r_{ij} \leftarrow \mathbb{F}_2; r_{ji} \leftarrow r_{ij}$ for $i = 0$ to $d - 1$ dofor $i = 0$ to $d - 1$ dofor $j = i + 1$ to $d - 1$ do $r_{ij} \leftarrow \mathbb{F}_2; r_{ji} \leftarrow r_{ij}$ for $i = 0$ to $d - 1$ do $j_i \leftarrow \begin{cases} 1 & \text{if } i = 0 \\ 0 & \text{otherwise} \end{cases}$ for $i = 0$ to $d - 1$ dofor $j = j_i$ then $r_{ij} \leftarrow \mathbb{F}_2; r_{ji} \leftarrow r_{ij}$ $p_{ij} \leftarrow \mathbb{R}(w_i \oplus (x_i \land PR(y_i)) \oplus (\overline{x_i} \land PR(r_{ij}))) \oplus$ for $i = 0$ to $d - 1$ do $R(x_i \land R(y_j \oplus r_{ij}))$ $\overline{x_i} \land PR(r_{ij})) \oplus (\overline{x_i} \land PR(r_{ij})) \oplus$ $\mathfrak{else}$ $p_{ij} \leftarrow \mathbb{R}(\overline{x_i} \land PR(r_{ij})) \lor \mathbb{R}(x_i \land R(y_j \oplus r_{ij}))$ $z_i \leftarrow \bigoplus_{j=0, j \neq i}^{d-1} p_{ij}$ $\mathbb{R}(y_i \oplus r_{ij}) \oplus (PR(x_i) \land R(y_j \oplus r_{ij}))$ $\mathfrak{else}$ $p_{ij} \leftarrow \mathbb{R}\left((x_i \land r_{ij}) \oplus r'_{ij}^{\prime}\right) \oplus (PR(x_i) \land R(y_j \oplus r_{ij}))$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Algorithm 6 HPC20 Toffoli gadget with d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Algorithm 7</b> HPC30 Toffoli gadget with $d$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output: Sharing z such that $z = w \oplus (x \land y)$ .Output: Sharing z such that $z = w \oplus (x \land y)$ .for $i = 0$ to $d - 1$ do<br>for $j = i + 1$ to $d - 1$ do<br>for $i = 0$ to $d - 1$ do<br>$r_{ij} \stackrel{<}{\leftarrow} \mathbb{F}_2; r_{ji} \leftarrow r_{ij}$ for $i = 0$ to $d - 1$ do<br>$r_{ij} \stackrel{<}{\leftarrow} \mathbb{F}_2; r_{ji} \leftarrow r_{ij}$ for $i = 0$ to $d - 1$ do<br>$r_{ij} \stackrel{<}{\leftarrow} \mathbb{F}_2; r_{ji} \leftarrow r_{ij}$ for $i = 0$ to $d - 1$ do<br>$r_{ij} \stackrel{<}{\leftarrow} \mathbb{F}_2; r_{ji} \leftarrow r_{ij}$ for $j = 0$ to $d - 1, j \neq i$ do<br>if $j = j_i$ then<br>$p_{ij} \leftarrow \mathbb{R}(w_i \oplus (x_i \land PR(y_i)) \oplus (\overline{x_i} \land PR(r_{ij}))) \oplus$ for $j = 0$ to $d - 1, j \neq i$ do<br>if $j = j_i$ then<br>$p_{ij} \leftarrow \mathbb{R}(\overline{w_i} \land PR(r_{ij})) \lor \mathbb{R}(x_i \land R(y_j \oplus r_{ij}))$ Output: Sharing z such that $z = w \oplus (x \land y)$ .else<br>$p_{ij} \leftarrow \mathbb{R}(\overline{w_i} \land PR(r_{ij})) \lor \mathbb{R}(x_i \land R(y_j \oplus r_{ij}))$ $\mathbb{R}(y_j \oplus r_{ij})$ $\mathbb{R}(w_i \oplus (x_i \land (y_i \oplus r_{ij})) \oplus r'_{ij}) \oplus (PR(x_i) \land R(y_j \oplus r_{ij}))$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | shares.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | shares.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $ \begin{split} & \text{for } j = i + 1 \text{ to } d - 1 \text{ do} & \text{for } j = i + 1 \text{ to } d - 1 \text{ do} \\ & r_{ij} \stackrel{\wedge}{\leftarrow} \mathbb{F}_2; r_{ji} \leftarrow r_{ij} & r_{ij} \stackrel{\wedge}{\leftarrow} \mathbb{F}_2; r_{ji} \leftarrow r_{ij} \\ & \text{for } i = 0 \text{ to } d - 1 \text{ do} & r_{ij} \stackrel{\wedge}{\leftarrow} \mathbb{F}_2; r_{ji} \leftarrow r_{ij} \\ & j_i \leftarrow \begin{cases} 1 & \text{if } i = 0 \\ 0 & \text{otherwise} \end{cases} & \text{for } i = 0 \text{ to } d - 1 \text{ do} \\ & r'_{ij} \stackrel{\wedge}{\leftarrow} \mathbb{F}_2; r'_{ji} \leftarrow r'_{ij} \\ & \text{for } i = 0 \text{ to } d - 1 \text{ do} \\ & for j = 0 \text{ to } d - 1, j \neq i \text{ do} \\ & \text{if } j = j_i \text{ then} \\ & p_{ij} \leftarrow \mathbb{R}(w_i \oplus (x_i \land PR(y_i)) \oplus (\overline{x_i} \land PR(r_{ij}))) \oplus \\ & \text{else} \\ & p_{ij} \leftarrow \mathbb{R}(\overline{x_i} \land PR(r_{ij})) \lor \mathbb{R}(x_i \land R(y_j \oplus r_{ij})) \\ & \text{else} \\ & p_{ij} \leftarrow \mathbb{R}(\overline{x_i} \land PR(r_{ij})) \lor \mathbb{R}(x_i \land R(y_j \oplus r_{ij})) \\ & \text{else} \\ & p_{ij} \leftarrow \mathbb{R}(\overline{x_i} \land PR(r_{ij})) \lor \mathbb{R}(x_i \land R(y_j \oplus r_{ij})) \\ & \text{else} \\ & p_{ij} \leftarrow \mathbb{R}(\overline{x_i} \land PR(r_{ij})) \lor \mathbb{R}(x_i \land R(y_j \oplus r_{ij})) \\ & \text{else} \\ & p_{ij} \leftarrow \mathbb{R}(\overline{x_i} \land PR(r_{ij})) \lor \mathbb{R}(x_i \land R(y_j \oplus r_{ij})) \\ & \text{for } f = 0 \text{ to } f = 0  to$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $z_i \leftarrow \bigoplus_{i=0, i \neq i}^{d-1} p_{ij}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{aligned} & \mathbf{for} \ j = i + 1 \ \mathbf{to} \ d - 1 \ \mathbf{do} \\ & r_{ij} \stackrel{\$}{\leftarrow} \mathbb{F}_2; \ r_{ji} \leftarrow r_{ij} \\ & \mathbf{for} \ i = 0 \ \mathbf{to} \ d - 1 \ \mathbf{do} \\ & j_i \leftarrow \begin{cases} 1 & \text{if} \ i = 0 \\ 0 & \text{otherwise} \end{cases} \\ & \mathbf{for} \ j = 0 \ \mathbf{to} \ d - 1, j \neq i \ \mathbf{do} \\ & \mathbf{if} \ j = j_i \ \mathbf{then} \\ & p_{ij} \leftarrow R(w_i \oplus (x_i \land PR(y_i)) \oplus (\overline{x_i} \land PR(r_{ij}))) \\ & R(x_i \land R(y_j \oplus r_{ij})) \\ & else \end{aligned}$ | $\begin{aligned} & \mathbf{for} \ j = i + 1 \ \mathbf{to} \ d - 1 \ \mathbf{do} \\ & r_{ij} \overset{\$}{\leftarrow} \mathbb{F}_2; \ r_{ji} \leftarrow r_{ij} \\ & r'_{ij} \overset{\$}{\leftarrow} \mathbb{F}_2; \ r'_{ji} \leftarrow r'_{ij} \\ & \mathbf{for} \ i = 0 \ \mathbf{to} \ d - 1 \ \mathbf{do} \\ & j_i \leftarrow \begin{cases} 1 & \text{if} \ i = 0 \\ 0 & \text{otherwise} \end{cases} \\ & \mathbf{for} \ j = 0 \ \mathbf{to} \ d - 1, j \neq i \ \mathbf{do} \\ & \text{if} \ j = j_i \ \mathbf{then} \\ & p_{ij} \leftarrow \mathbb{R} \left( w_i \oplus (x_i \land (y_i \oplus r_{ij})) \oplus r'_{ij} \right) \oplus (PR (x_i) \land \\ & \mathbb{R} (y_j \oplus r_{ij})) \\ & \text{else} \\ & p_{ij} \leftarrow \mathbb{R} \left( (x_i \land r_{ij}) \oplus r'_{ij} \right) \oplus (PR (x_i) \land R (y_j \oplus r_{ij})) \end{aligned}$ |

Regarding the security analysis, there is no change to the leakage, except for the addition or removal of registers that are not needed for security purposes (the original security proofs of HPC2 and HPC3 did not assume the presence of these registers, and adding registers can only make the adversary weaker).

# 5 Optimized Gadgets: HPC2o and HPC3o

#### 5.1 New Gadget Designs

In this section, we go beyond the register re-use of Section 4 by completely eliminating some pipeline registers through optimizations inside the AND gadgets.

**Inner-domain term optimization** Instead of separating the inner-domain terms in HPC2 and HPC3, we propose to merge these terms with cross-domain terms. For HPC2, we modify Algorithm 2 as follows. For every i = 0, ..., d-1, we select an arbitrary  $j_i \neq i$  (e.g.,  $j_i = 0$  for all  $i \neq 0$ , and  $j_0 = 1$ ). Then, we replace the computation  $R(\overline{x_i} \land PR(r_{ij_i}))$  with  $R((x_i \land PR(y_i)) \oplus (\overline{x_i} \land PR(r_{ij_i})))$  (see Algorithm 6), which integrates the term  $x_i \land y_i$ into the term  $p_{ij_i}$ . This transformation removes d registers from the HPC2 gadget and does not damage the security: for the PINI security analysis, we added a term of the domain i to a term that already involves the domain i (see proof in Appendix A).

For HPC3 (Algorithm 3), we first apply a simplification to the gadget, by remarking that the NOT gate in the computation  $R((\overline{x_i} \wedge r_{ij}) \oplus r'_{ij}) \oplus PR(x_i) \wedge R(y_j \oplus r_{ij})$  can be removed. Namely, replacing this computation with  $R((x_i \wedge r_{ij}) \oplus r'_{ij}) \oplus PR(x_i) \wedge R(y_j \oplus r_{ij})$  still leads to a correct gadget: while the original computation results in the value  $(x_i \wedge y_j) \oplus r'_{ij} \oplus r_{ij}$  and the new one gives  $(x_i \wedge y_j) \oplus r'_{ij}$ , both lead to a correct gadget (i.e., the output is a sharing of  $x \wedge y$ ). Regarding the security, the core observation is that, similarly to the original gadget, the new computation  $R((x_i \wedge r_{ij}) \oplus r'_{ij})$  has the distribution of a fresh random value if  $r'_{ij}$  is not observed elsewhere. In other words, the cancellation of the random  $r_{ij}$  has no security impact. While the removal of a NOT gate in the gadget has no significant performance impact by itself<sup>7</sup>, it becomes useful when optimizing the inner-domain terms. Indeed, we can apply a similar optimization to HPC2 by turning  $R((x_i \wedge r_{ij_i}) \oplus r'_{ij_i})$  into  $R((x_i \wedge (y_i \oplus r_{ij_i})) \oplus r'_{ij_i})$ , which additionally saves one AND gate (see Algorithm 7).

Finally, we remark that, where  $x_i y_i$  is computed, a share  $w_i$  of a third input w can be XORed without breaking the PINI property (intuitively, this is because the set of manipulated "share domains" is not changed). This addition turns the HPC20 and HPC30 gadgets into Toffoli gadgets, saving pipeline registers for  $w_i$ . The final gadgets are given in Algorithm 6 and Algorithm 7, their performance characteristics are listed in Table 1 and their formal security proofs are given in Appendix A.<sup>8</sup> The new gadgets have the same functionality as the AND-XOR gadgets of [WFP<sup>+</sup>23], but are more efficient.<sup>9</sup>

**Gate area optimization** We introduce another optimization in the HPC2 gadget. In the computation of  $p_{ij}$  for  $j \neq j_i$  and  $j \neq i$  (i.e., for the cross-domain terms where the above optimization is not applied),  $R(\overline{x_i} \wedge PR(r_{ij}))$  and  $R(x_i \wedge R(y_j \oplus r_{ij}))$  are never both 1. Therefore, combining these terms with an XOR gate gives the same results as combining them with a OR gate, which has a lower area in CMOS designs. This optimization is implemented in Algorithm 6.

#### 5.2 Using Toffoli Gates in Compress

COMPRESS takes as input circuits composed of AND, XOR and NOT gates. Therefore, in order to efficiently make use of the HPC20 and HPC30 gadgets, it should extract Toffoli gates from a circuit of AND and XOR gates.

We use the following approach. For each output sharing a of an AND gate, if a is XORed with b ( $c = a \oplus b$ ) and not used in any other gate, then we may instantiate a Toffoli gate with b as the third (w) input. Further, if c is itself used only once in an XOR with d, then d (or  $c \oplus d$ ) is also a good candidate as an input to a Toffoli gate. This continues, until the value is not used in an XOR, or if it is an operand of more than one operation (we do not want to force logic duplication). All these variables can be XORed into the input of the Toffoli gate that contains the AND computation of a, which may save pipelining registers. However, some of these variables could be more efficiently computed at a later cycle, and we should not adopt a restrictive all-or-none approach. We therefore consider that a subset of these variables may be XORed in the input of the Toffoli gate,

<sup>&</sup>lt;sup>7</sup>Let us remark that removing the NOT gate makes the gadget trivially generalizable to any field (our security proof is field-agnostic, provided that the gadget is made correct by turning XOR gates into additions and subtractions where needed, and turning AND gates into products). The change also makes the randomness  $r_{ij}$  local [CGZ20] to the gadget, which might help with masking randomness re-use, but is beyond the scope of this work.

$<sup>^8\</sup>mathrm{As}$  a sanity-check (and also to avoid implementation bugs), our implementations of HPC20 and HPC30 have been verified with SILVER [KSM20] for d=2,3.

<sup>&</sup>lt;sup>9</sup>Actually the AND-XOR gadgets share the registers between the  $w_i$  and  $x_i y_i$  terms. However, they do not share these registers with cross-domain terms, as is done in HPC20 and HPC30.

| Algorithm 8 Identification of Toffoli gates in Boolean circuit                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Input:</b> A Boolean circuit, $g$ a AND gate in the circuit.<br><b>Output:</b> $(L_g, R_g)$ where $L_g$ is a set of XOR-operands for a Toffoli gate instantiation and $R_g$ .<br>for all AND gates $g$ in the circuit do |

| Let $\boldsymbol{z}$ be the output of $g$ .                                                                                                                                                                                 |

| $o \leftarrow z$<br>while <i>o</i> is the operand of only one operation <b>do</b><br>Let <i>o</i> be the output of that operation.                                                                                          |

| $R_g \leftarrow o$ $\triangleright o$ is now the "result" variable.                                                                                                                                                         |

| $S \leftarrow \{ o \}$                                                                                                                                                                                                      |

| $L_g \leftarrow \emptyset$                                                                                                                                                                                                  |

| $\begin{array}{l} \text{if } \boldsymbol{o} \neq \boldsymbol{z} \text{ then} \\ \text{while } S \neq \emptyset \text{ do} \end{array}$                                                                                      |

| Pop an element $\boldsymbol{x}$ from S                                                                                                                                                                                      |

| if $\boldsymbol{x}$ is the output of an XOR gate $g'$ and $\boldsymbol{x}$ is the operand of only one operation then<br>Add the operands of $g'$ to $S$ .                                                                   |

| else                                                                                                                                                                                                                        |

| Add $\boldsymbol{x}$ to $L_g$ .                                                                                                                                                                                             |

while others may be XORed to its output. Further, if  $d = e \oplus f$  and d is only used once in the circuit, then we should take e and f in our list of XOR operands instead of d, in order to maximize flexibility and avoid dependency on the parentheses between the additions in original circuit representation.

The flow of COMPRESS is therefore modified as follows. First, for every AND gate in the circuit, Algorithm 8 is executed in order to identify a list of variables that are candidates to be XORed in a Toffoli gate, and the name of a "result" variable, that is, the XOR of all these variables and of the output of the AND gate. Next, we add an alternative way of computing the result (we keep the approach without Toffoli gate as a solution). This alternative way is based on an extended Toffoli gate, which takes as input the operands of the AND gate and the variables in the candidates list, and it outputs the result.

By introducing multiple computations inside a single extended Toffoli gadget, we go against our previous decomposition approach and, as a result, could lose some scheduling optimizations of COMPRESS. We circumvent this issue by making the extended Toffoli gadget very flexible w.r.t. input and output latency, and by providing COMPRESS the knobs to exploit this flexibility (as well as information on the cost of the gadget depending on how it is used). In more details, the Toffoli gadgets take inputs sharings  $\boldsymbol{x}, \boldsymbol{y}$  and  $(\boldsymbol{w}_i)_i$ . They are based on the HPC20 or the HPC30 gadget, whose input  $\boldsymbol{w}$  is the XOR of a subset of the sharings  $\boldsymbol{w}_i$  (computed using XOR gadgets). The output  $\boldsymbol{z}$  of the HPC20/HPC30 gadget is then forwarded to an arbitrary (subject to optimization) stage deeper in the pipeline by means of registers. In the pipeline stages covered by these registers, the other  $\boldsymbol{w}_i$  operands are XORed to the forwarded state (again, the staging of these XOR operations is selected by the optimization solver).

## 6 Case Studies

In this section, we look at the performance characteristics of the masked pipelines generated by COMPRESS and we compare them to the state-of-the-art designs. The area numbers are obtained by synthesizing the designs with Yosys 0.33 and the Nangate 45 PDK, while the latency for S-boxes and adders is the number or register layers.

#### 6.1 Optimized S-boxes

As a first case study for COMPRESS, we generated optimized implementations of the AES S-box and of the 8-bit Skinny S-box. For the AES S-box, we considered two of the most commonly-used and state-of-the-art representations for masking: the 34 AND gate Boyar-Peralta representation [BP12] and the Canright tower field representation [Can05], while

| Security<br>order | Latency | Design               | Random<br>bits | Area w/o PRNG<br>(kGE) | Area w/ PRNG<br>(kGE) |

|-------------------|---------|----------------------|----------------|------------------------|-----------------------|

|                   |         | Base                 |                | 3.53                   | 5.34                  |

|                   | 4       | $\operatorname{Sep}$ | 46             | 3.24                   | 5.05                  |

|                   |         | Opt                  |                | 2.78                   | 4.59                  |

| -                 |         | Base                 |                | 3.81                   | 5.26                  |

| 1                 | 5       | $\operatorname{Sep}$ | 37             | 3.51                   | 4.97                  |

|                   |         | Opt                  |                | 3.08                   | 4.54                  |

|                   |         | Base                 |                | 4.06                   | 5.40                  |

|                   | 6       | $\operatorname{Sep}$ | 34             | 3.77                   | 5.11                  |

|                   |         | Opt                  |                | 3.34                   | 4.67                  |

|                   |         | Base                 |                | 7.91                   | 13.34                 |

|                   | 4       | Sep                  | 138            | 7.47                   | 12.90                 |

|                   |         | Opt                  |                | 6.79                   | 12.22                 |

|                   |         | Base                 |                | 8.54                   | 12.91                 |

| 2                 | 5       | Sep                  | 111            | 8.10                   | 12.47                 |

|                   |         | Opt                  |                | 7.47                   | 11.84                 |

|                   |         | Base                 |                | 9.00                   | 13.01                 |

|                   | 6       | $\operatorname{Sep}$ | 102            | 8.56                   | 12.57                 |

|                   |         | Opt                  |                | 7.92                   | 11.94                 |

|                   |         | Base                 |                | 14.03                  | 24.89                 |

|                   | 4       | Sep                  | 276            | 13.44                  | 24.30                 |

|                   |         | Opt                  |                | 12.96                  | 23.82                 |

|                   |         | Base                 |                | 15.17                  | 23.91                 |

| 3                 | 5       | Sep                  | 222            | 14.58                  | 23.32                 |

|                   |         | Opt                  |                | 14.14                  | 22.87                 |

|                   |         | Base                 |                | 15.87                  | 23.90                 |

|                   | 6       | $\operatorname{Sep}$ | 204            | 15.28                  | 23.31                 |

|                   |         | Opt                  |                | 14.88                  | 22.91                 |

|                   |         | Base                 |                | 21.89                  | 40.00                 |

|                   | 4       | $\operatorname{Sep}$ | 460            | 21.15                  | 39.26                 |

|                   |         | Opt                  |                | 20.45                  | 38.55                 |

|                   |         | Base                 |                | 23.68                  | 38.25                 |

| 4                 | 5       | $\operatorname{Sep}$ | 370            | 22.95                  | 37.51                 |

|                   |         | Opt                  |                | 22.24                  | 36.80                 |

|                   |         | Base                 |                | 24.69                  | 38.07                 |