# Automated Generation of Fault-Resistant Circuits

Nicolai Müller<sup>1</sup> and Amir Moradi<sup>2</sup>

<sup>1</sup> Ruhr University Bochum, Horst Görtz Institute for IT Security, Bochum, Germany firstname.lastname@rub.de

<sup>2</sup> Technische Universität Darmstadt, Darmstadt, Germany firstname.lastname@tu-darmstadt.de

Abstract. Fault Injection (FI) attacks, which involve intentionally introducing faults into a system to cause it to behave in an unintended manner, are widely recognized and pose a significant threat to the security of cryptographic primitives implemented in hardware, making fault tolerance an increasingly critical concern. However, protecting cryptographic hardware primitives securely and efficiently, even with wellestablished and documented methods such as redundant computation, can be a timeconsuming, error-prone, and expertise-demanding task. In this research, we present a comprehensive and fully-automated software solution for the Automated Generation of Fault-Resistant Circuits (AGEFA). Our application employs a generic and extensively researched methodology for the secure integration of countermeasures based on Error-Correcting Codes (ECCs) into cryptographic hardware circuits. Our software tool allows designers without hardware security expertise to develop fault-tolerant hardware circuits with pre-defined correction capabilities under a comprehensive fault adversary model. Moreover, our tool applies to masked designs without violating the masking security requirements, in particular to designs generated by the tool AGEMA. We evaluate the effectiveness of our approach through experiments on various block ciphers and demonstrate its ability to produce fault-tolerant circuits. Additionally, we assess the security of examples generated by AGEFA against Side-Channel Analysis (SCA) and FI using state-of-the-art leakage and fault evaluation

Keywords: Fault Analysis · Impeccable Circuits · SIFA · Hardware · Masking

#### 1 Introduction

The already well-advanced integration of embedded systems into our daily lives highlights the critical need for reliable guarantees with respect to the confidentiality of sensitive data processed by these systems. Cryptographic primitives, such as block ciphers, are well-established methods that ensure the confidentiality of data both at rest and in transit. However, the implementation of cryptographic primitives in hardware presents significant challenges that are yet to be fully resolved. Physical attacks, such as passive Side-Channel Analysis (SCA) attacks [Koc96] and active Fault Injection (FI) attacks [BDL97], have emerged as severe attack vectors due to the physical accessibility that embedded devices offer to potential adversaries.

In the context of SCA, an adversary records a certain physical characteristic of the device during the execution of a cryptographic primitive and subsequently exploits the relation between the measurements and the processed data to recover secret information. Examples include but are not restricted to [Koc96, KJJ99, GMO01, HS13, GST14].

Masking [CJRR99], as a well-studied countermeasure against SCA based on secret sharing [Sha79], has gained a considerable amount of attention from the scientific community due to its simple security assumptions and adversary models. The d-probing model [ISW03] and its extension to cover physical defaults, known as the robust probing model [FGP<sup>+</sup>18], are the commonly used adversary models and form the basis for security notions such as probing security and composability, which enable to prove the formal security of masked implementations. However, designing and implementing a properly masked cryptographic primitive is complex, error-prone, and tedious. Many examples of insecure masking schemes can be found in the literature [MMSS19], highlighting the need for automated solutions that reduce manual interaction and the potential for human error. One such solution is the Automated Generation of Masked Hardware (AGEMA) [KMMS22], which automates the generation of masked hardware circuits by translating unprotected gate-level netlists into masked hardware circuits albeit with an associated increase in circuit size and latency compared to manually crafted masked designs. To narrow the performance gap in terms of area and latency between automatically-generated masked designs and manual approaches, various optimizations have been introduced and implemented into new software tools like the Automated Generation of Masked Nonlinear Components (AGMNC) [WFP+23] or Compress [CGM $^+23$ ].

In addition to passive SCA attacks, active adversaries employ techniques that deliberately introduce faults into the operation of the device to compromise its security [BDL97]. Such attacks can be carried out through various fault injection methods, i.e. by shortening the period of particular clock cycles (clock-glitching) [ADN+10], by altering the power supply (voltage-glitching) [SGD08], by electromagnetic pulses (as Electromagnetic Fault Injection (EMFI)) [SSAQ02], or by focused laser beams [SA02]. The injected faults can be exploited by a various set of concrete techniques including Differential Fault Analysis (DFA) [BS97], Differential Fault Intensity Analysis (DFIA) [GYTS14], Statistical Fault Attack (SFA) [FJLT13], Fault Sensitivity Analysis (FSA) [LSG+10], Ineffective Fault Attack (IFA) [Cla07], and Statistical Ineffective Fault Attack (SIFA) [DEK<sup>+</sup>18]. The first generic and comprehensive hardware fault adversary model in [RSG23] abstracts any fault, regardless of its location, type, or timing, by replacing a gate whose output is faulty with another gate realizing the functionality of the faulty gate. The faulty circuit is then compared with a fault-free circuit to determine whether the fault is propagated to the primary output. Incorporating redundancy into the system can be an effective strategy for countering FI attacks. This redundancy allows faulty states to be compared with fault-free states, thereby detecting or correcting faults introduced during the attack. One way of incorporating redundancy is to use binary linear codes, which can be implemented in a variety of ways. Importantly, the fault tolerance of an implementation depends on the specification of the underlying code used.

- Schemes based on Error-Detecting Codes (EDCs) are used to detect a pre-defined number of faults. If a fault is detected, the device discards the faulty output and may eliminate the key if a certain threshold is reached [AMR<sup>+</sup>20].

- Schemes based on Error-Correcting Codes (ECCs) are used to correct a pre-defined number of faults. Hence, an adversary will always observe fault-free outputs as long as the injected fault is covered by the underlying fault model, defined by the employed code [SRM20].

Since EDC-based schemes do not protect against SIFA [DEK<sup>+</sup>18], this work focuses on the application of ECC-based schemes to block ciphers, as exemplarily and manually done in [SRM20].

#### **Our Contributions**

To the best of our knowledge, there is no AGEMA-equivalent tool for protecting a given design against FI attacks, i.e. there is no tool for automatically generating fault-tolerant circuits. We fill this gap by introducing an extension to the current security-aware hardware design flow, namely Automated Generation of Fault-Resistant Circuits (AGEFA). In particular, our tool, which is publicly available via GitHub<sup>1</sup>, has the following key features.

- AGEFA enables the fully automated translation of unprotected hardware designs, i.e. designs without any countermeasures against FI, into provably fault-tolerant hardware circuits. In particular, the fault-tolerance of AGEFA's outputs, even against SIFA, can be exhaustively verified by cryptographic fault-analysis tools, e.g., VerFI [AWMN20]. For this work, we have chosen to exclusively focus on symmetric ciphers, aiming to ensure a comprehensive verification process. While there are no inherent limitations to applying AGEFA to, e.g., post-quantum cryptography, the potentially extensive outcomes would pose significant challenges for verification. As a result, AGEFA enables even inexperienced engineers without deep knowledge in the field of hardware security to reliably protect any design against FI attacks. Concretely, AGEFA provides automated solutions for the following problems:

- Searching for an efficient ECC that is not only correct but also tailored precisely to the designer's specific requirements can be a time-consuming task when approached manually. In Section 3.2, we present an automated procedure aimed at expediting the process of finding an efficient ECC tailored to the individual requirements of the user.

- Implementing a fault-resistant design, which relies on the generated ECC, is a task fraught with a high risk of implementation flaws. Even minor oversights can compromise the security of the entire design. In Section 3.3, we outline a procedure that automates the implementation process, thereby eliminating human errors.

- Furthermore, AGEFA can incorporate several non-trivial optimizations, typically

performed manually. This capability enables the generated designs to achieve

an efficiency level comparable to that of manually crafted designs.

- When AGEFA processes a masked design, e.g. an SCA-secure design generated by AGEMA, it preserves all the security guarantees provided by the masking countermeasure that satisfy Probe-Isolating Non-Interference (PINI) requirements, while adding protection against FI attacks. In practice, this means that an engineer can give an unprotected design without any countermeasures to AGEMA first, and receive an SCA-secure design based on PINI gadgets. Further processing of the resulting design with AGEFA will produce a solution that is SCA- and FI-secure.

# 2 Background

#### 2.1 Notations

As summarized in Table 1, we use lower-case characters to denote atomic elements, e.g. Boolean variables, and sans-serif fonts to denote Boolean functions. Additionally, we use upper-case bold characters, such as  $\mathbf{X}$ , to represent a set of elements with cardinality  $|\mathbf{X}|$ . We refer to the individual elements of a set using their index, such that  $x_i \in \mathbf{X}$  represents

<sup>&</sup>lt;sup>1</sup>https://github.com/Chair-for-Security-Engineering/AGEMA

| Notation                                                                                                              | Description                                                                                       | Variable                                        | Description                                                     |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------|

|                                                                                                                       | n-ary Boolean function<br>n-ary vectorial Boolean function<br>n-ary i-th coordinate function of F | $d \\ g \\ t$                                   | Security order Glitch coverage Transition coverage              |

| $x \in \mathbb{F}_2$ $X \in \mathbb{F}_2^n$ $x_i \in \mathbb{F}_2$ $\mathbf{X}$                                       | Boolean variable Vector of $n$ Boolean variables $i$ -th Boolean variable of $X$ Set              | $\begin{array}{c} c \\ f \\ s \\ l \end{array}$ | Coupling coverage  Fault cardinality Fault style Fault location |

| $\underline{\underline{P}} \in \mathbb{F}_2^{n \times m}$ $\underline{\underline{I}}_n \in \mathbb{F}_2^{n \times n}$ | $(n \times m)$ -matrix Identity matrix of size $n$                                                | $k \\ n \\ \delta$                              | Message size Codeword size Minimum distance                     |

| $\mathcal{M}$                                                                                                         | Module                                                                                            |                                                 | Minimum distance                                                |

**Table 1:** Notations used in this work.

**Table 2:** Parameters associated with a single wire.

| Notation                      | Description                                                                                                                                                                                                                      |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\operatorname{attribute}(w)$ | Returns the attribute associated with $w$ . It holds that $\mathtt{attribute}(w) \in \{\mathtt{clock}, \mathtt{control}, \mathtt{layer}, \mathtt{reset}, \mathtt{secure}\}$ introduced in Section 3.                             |

| ${\tt share\_domain}(w)$      | If $w$ carries the share of a sensitive variable, this parameter stores the share domain of $w$ . This is introduced in Section 3.1.                                                                                             |

| ${\tt linear\_index}(w)$      | If $w$ is the input or output of a binary matrix with elements in $\mathbb{F}_2^k$ we enumerate all $k$ -bit input and output chunks and store the number related to $w$ as its linear index. This is introduced in Section 3.1. |

the *i*-th element of **X**. Exceptionally, we use upper-case characters to denote multi-bit variables such as  $X \in \mathbb{F}_2^n$ .

#### 2.2 Circuit Model

We formalize the operations carried out by a hardware circuit through a Boolean function  $\mathbb{F}_2^i \to \mathbb{F}_2^p$  with i inputs and o outputs. The circuit acquires every input through a signal driven by a physical wire. Subsequently, the corresponding outputs are retrieved from the circuit by reading the signals transmitted through the output wires. Each wire w in a circuit is uniquely defined by its name while we refer to the signal currently transmitted by a wire as its state. Formally, we associate multiple parameters with each wire and define functions to access them as given in Table 2.

Further, review a circuit as a composition of separate building blocks called modules.

**Definition 1** (Module). A module  $\mathcal{M}$  defines a quadruple ( $\mathbf{IN}_{\mathcal{M}}, \mathbf{T}_{\mathcal{M}}, \mathbf{OUT}_{\mathcal{M}}, \mathbf{INST}_{\mathcal{M}}$ ) with the following elements:

- $IN_{\mathcal{M}}$  (resp.  $OUT_{\mathcal{M}}$ ) defines a set of primary input wires (resp. primary output wires) belonging to  $\mathcal{M}$ .

- $\mathbf{T}_{\mathcal{M}}$  defines the set of intermediate (internal) wires of  $\mathcal{M}$ .

- $\mathbf{INST}_{\mathcal{M}}$  defines a set of instructions representing the functionality of the  $\mathcal{M}$ . We define an instruction as a Boolean function based on a restricted set of operands {not, and, nand, or, nor, xor, xnor, reg}.

We refer to an atomic module  $\mathcal{G}$  as a gate (either combinational or sequential). Every gate evaluates a single output ( $|\mathbf{OUT}_{\mathcal{G}}| = 1^2$ ) by applying a single operation from {not, and, nand, or, nor, xor, xnor, reg} to the signals in  $\mathbf{IN}_{\mathcal{G}}$ , i.e.  $\mathbf{T}_{\mathcal{G}} = \emptyset$ .

<sup>&</sup>lt;sup>2</sup>Note that, for this work, we exclude gates with multiple outputs and do not use the inverted output of a register. This restriction is related to the use of AGEMA.

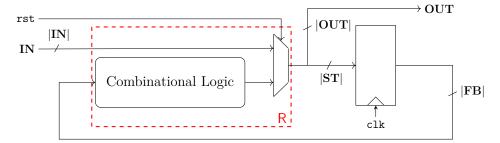

**Figure 1:** General Mealy model of a synchronous sequential circuit.

**Example 1.** Let  $\mathcal{M}$  be a module that abstracts multiple gates computing the Boolean function  $z = ab \oplus c$ . Then, it holds that  $\mathbf{IN}_{\mathcal{M}} = \{a, b, c\}$  and  $\mathbf{OUT}_{\mathcal{M}} = \{z\}$ . There are multiple possibilities to construct  $\mathbf{INST}_{\mathcal{M}}$  such as  $\mathbf{INST}_{\mathcal{M}} = \{z = a \text{ and } b \text{ xor } c\}$  with  $\mathbf{T}_{\mathcal{M}} = \emptyset$  or  $\mathbf{INST}_{\mathcal{M}} = \{q = a \text{ and } b, z = q \text{ xor } c\}$  with  $\mathbf{T}_{\mathcal{M}} = \{q\}$ . Further, we can represent  $\mathcal{M}$  as a composition of  $\mathcal{G}_{\mathsf{and}} = (\{a, b\}, \emptyset, \{z\}, \{z = a \text{ and } b\})$  and  $\mathcal{G}_{\mathsf{xor}} = (\{a, b\}, \emptyset, \{z\}, \{z = a \text{ xor } b\})$ .

**Definition 2** (Circuit). We model a circuit as a directed graph  $(\mathbf{G}, \mathbf{W})$  while each vertex  $\mathcal{G} \in \{\mathcal{G}_{\mathsf{not}}, \mathcal{G}_{\mathsf{and}}, \mathcal{G}_{\mathsf{nand}}, \mathcal{G}_{\mathsf{or}}, \mathcal{G}_{\mathsf{nor}}, \mathcal{G}_{\mathsf{xnor}}, \mathcal{G}_{\mathsf{reg}}\}$  represents an atomic module, e.g. a sequential or combinational gate, and each edge  $w \in \mathbf{W}$  represents a wire.

We focus on sequential circuits, where a clock signal clk synchronizes the processed data by storing the state of wires in **ST** in registers. Any synchronous sequential circuit (which has no combinational loops) can be modeled as a Mealy machine [Mea55]. We show the schematic model of a generic sequential circuit in Figure 1.

The model incorporates a single register stage created by merging all synchronization elements, such as registers from an arbitrary number of stages. Initially, an active reset signal rst forces the register stage to load the state of the primary inputs (data and control signals) carried by wires in IN. Subsequently, the circuit repeatedly processes the state of ST by feeding the feedback signal state carried by wires in FB back to the combinational logic. The register stage synchronizes the state of all wires in ST using a clock signal clk while the combinational logic computes the subsequent register inputs based on signals from FB. We refer to the combinational logic together with its subsequent multiplexer as the round function R.

#### 2.3 Security Models

The discussion on security models in our work is twofold, encompassing both the SCA and FI adversary models. We remark, that SCA adversary models allow us to prove the secure application of masking [CJRR99] which stands as the predominant concept for protecting a circuit against SCA. Therefore, masking is the only SCA countermeasure considered in this work. According to secret sharing [Sha79], masking involves randomizing every sensitive variable  $X \in \mathbb{F}_2^n$  with d+1 uniformly and randomly distributed shares  $X^0, \ldots, X^d \in (\mathbb{F}_2^n)^{d+1}$  satisfying  $X = \bigoplus_{i=0}^d X^i$ . In addition, the circuit must undergo transformation into a masked variant, executing every operation on a subset of shares. However, while we briefly revisit SCA models to provide necessary background information, we focus more extensively on the FI adversary models.

#### 2.3.1 Side-Channel Analysis (SCA) Adversary Model

The d-probing adversary model [ISW03] restricts the adversary's capabilities to place a maximum of d probes on the wires of an ideal circuit. Each probe provides access to the

intermediate value of a specific wire at a particular point in time, corresponding to a clock cycle.

**Definition 3** (*d*-probing security). A circuit is *d*-probing secure iff it does not disclose any sensitive information to any *d*-probing adversary.

Further, the (g,t,c)-robust d-probing model [FGP<sup>+</sup>18] extends the d-probing model with the coverage of physical defaults, such as glitches (g), transitions (t), and couplings (c). A (g,t,c)-robust d-probing adversary can place up to d extended probes, each capable of recording all intermediate values on a specific wire that could potentially be leaked due to the physical defaults.

**Definition 4** ((g,t,c)-robust d-probing security). A circuit is (g,t,c)-robust d-probing secure iff it does not disclose any sensitive information to any (g,t,c)-robust d-probing adversary.

We remark that the most prominent instances of the robust probing model are the (1,0,0)-robust d-probing model, i.e. the glitch-extended probing model, (0,1,0), i.e. the transition-extended probing model, and (1,1,0), i.e. the glitch- and transition-extended probing model. Except [CBG<sup>+</sup>17, CEM18], couplings are not extensively considered particularly from a theoretical point of view due to the necessity to have access to the detailed information about the physical realization of the target device, e.g., place and routing details.

#### 2.3.2 Composability

As designs have continued to increase in complexity, it has become challenging to design and evaluate circuits that are provably robust-probing secure, especially those that require higher-order security. To address this issue, researchers have introduced *composable gadgets* [CGLS21], which are small and provably secure building blocks that can be composed to create circuits of any order that are also provably secure. In practice, tools such as AGEMA replace unprotected cells with their protected counterparts, i.e. gadgets.

**Definition 5** (Composability). A robust-probing secure gadget is composable iff its arbitrary composition with other robust-probing secure and composable gadgets also results in a robust-probing secure circuit.

For a set of gadgets to be composable, each gadget must individually satisfy particular security requirements, and all possible combinations of the gadgets must also be in conformity with the underlying security model. As explained in detail below, PINI [CS20] is known as one of such composable security notions.

**Definition 6** (Perfect Probe Simulation). Let  $\mathbf{P}$  be a set of d (extended) probes on a gadget.  $\mathbf{P}$  can be perfectly simulated with a set  $\mathbf{S}$  of input shares if a probabilistic polynomial-time simulator can be found that computes a joint probability distribution based on  $\mathbf{S}$ , which is identical to the distribution of  $\mathbf{P}$ .

**Definition 7** (*d*-Probe-Isolating Non-Interference (PINI)). Let **P** be a set of  $d_0$  (extended) probes on a gadget, and **S** a set of  $d_1$  (extended) probes on the gadget's primary outputs, while **O** contains all output share indices probed by the probes in **S**. A gadget is *d*-PINI iff for every  $\mathbf{P} \cup \mathbf{S}$  with  $d_0 + d_1 \leq d$ , there exists a set **I** of  $d_0$  share indices such that the wires probed by probes in  $\mathbf{P} \cup \mathbf{S}$  can be perfectly simulated from input shares with indices in  $\mathbf{I} \cup \mathbf{O}$  [CS20].

#### 2.3.3 Fault Injection (FI) Adversary Model

Based on [RSG23], we consider a formal model for the adversary whose abilities are denoted by  $\zeta(f,s,l)$ , where  $f \in \{1,2,\ldots,|\mathbf{G}|\}$  denotes the maximum number of faults that can be simultaneously injected into different gates,  $s \in \{\tau_{sr},\tau_s,\tau_r,\tau_{bf},\tau_{fm}\}$  the fault type i.e. stuck-at  $(\tau_{sr},\tau_s,\tau_r)$ , bit-flip  $(\tau_{bf})$ , or custom  $(\tau_{fm})$  faults, and  $l \in \{c_i,m,mc_i\}$  the possible fault locations, which are usually a restricted set of gates, defined by  $l = c_i \subseteq c_{\infty}$ , and registers, defined by l = m. In this work, we focus on a conservative (worst-case) adversary model that allows toggle faults  $(s = \tau_{bf})$ , including stuck-at faults as well, at arbitrary locations of the circuit, such as gates and registers  $(l = mc_{\infty})$ ,but excluding primary signals<sup>3</sup>. Each fault is modeled by replacing the faulty cell with a predefined cell that implements another functionality, i.e. for  $s = \tau_{bf}$  a faulty gate gets replaced by its negated variant. Hence, for certain given inputs X, the faulty circuit may produce a faulty intermediate state  $\tilde{Q}$  instead of Q while for other inputs the fault gets suppressed. Then, the model compares the primary output of the faulty circuit  $\tilde{Z}$  with that of an equivalent circuit without any fault Z to determine whether the injected fault was effective (cf. Definition 8) or ineffective (cf. Definition 9).

**Definition 8** (Effective fault). We consider an injected fault as effective, w.r.t to a primary input X, iff  $\tilde{Z} \neq Z$ , i.e. if the injected fault affects the primary output when X is processed.

**Definition 9** (Ineffective fault). We consider an injected fault as ineffective, w.r.t to a primary input X, iff  $\tilde{Z} = Z$ , i.e. if the injected fault does not affect the primary output when X is processed.

As our focus is solely on error correction, we can disregard separate definitions of detected and undetected faults. We consider a circuit to be secure under a fault model  $\zeta(f,t,l)$  if all the considered faults will be corrected, i.e. are ineffective.

**Definition 10** ((f, s, l)-fault security). A circuit is (f, s, l)-fault secure if all considered faults are ineffective.

We remark that  $(f, \tau_{bf}, mc_{\infty})$ -fault security, which we consider in this work, is equivalent to security under the multivariate adversary model defined in [SRM20] and that security according to Definition 10 also implies security against SIFA.

#### 2.3.4 Fault Propagation and Independence

Whenever an adversary injects faults in f intermediate gates, it is possible that more than f output signals of the circuit can become faulty [AMR<sup>+</sup>20]. To illustrate, let us assume that the adversary injects a fault in one intermediate gate inside the circuit. The faulty output of the gate may become the input of multiple subsequent gates, which are driven by the faulty gate propagating to multiple primary outputs. This phenomenon is known as fault propagation. To prevent fault propagation, every module must satisfy the independence property [AMR<sup>+</sup>20], meaning that every intermediate wire in a module should contribute to at most one primary output of the circuit.

**Definition 11** (Independence). The implementation of a module  $\mathcal{M}$  inside a circuit fulfills the independence property iff  $|\mathbf{OUT}_{\mathcal{M}}| = 1$ , i.e. if  $\mathcal{M}$  computes a single output.

If the independence property is satisfied, every introduced fault can make at most one output signal faulty.

$<sup>^3</sup>$ Faults on primary inputs without any redundancy cannot be detected or corrected.

#### 2.4 Countermeasures

#### 2.4.1 Error-Correcting Codes (ECCs)

To achieve (f, s, l)-fault security an error-correction mechanism is required. Usually, error-correction is based on redundancy and binary linear codes.

**Definition 12** (Binary linear code). A binary linear code  $\mathbf{C}$  is a k-dimensional subset of  $\mathbb{F}_2^n$  representing a linear and injective mapping function  $\mathbf{C}: \mathbb{F}_2^k \mapsto \mathbb{F}_2^n$ , i.e.  $\mathbf{C}$  applies  $\mathbf{C}$  to encode a message  $X \in \mathbb{F}_2^k$  to a codeword  $Y \in \mathbf{C}$ .

As C is linear, we can formalize the mapping by a  $(k \times n)$ -matrix, referred to as generator  $matrix \ \underline{G}$ , i.e. it holds that  $X \cdot \underline{G} = Y$ . Furthermore, we refer to a code as systematic iff it embeds the message into the first k bits of the codeword, i.e.  $\underline{G}$  is of the form  $[I_k|\underline{P}]$ , with  $\underline{I_k}$  being the  $k \times k$  identity matrix. In this context, where we are dealing with binary linear systematic codes (denoted as [n,k]-codes in the following), we refer to the codeword associated with the message  $X \in \mathbb{F}_2^k$  as  $Y = \langle X|X' \rangle \in \mathbf{C}$  while X' denotes the parity of X. Formally, the parity is computed as  $X' = X \cdot \underline{P}$ , while  $\underline{P}$  again is the matrix representation of a linear and injective mapping  $\mathsf{P} : \mathbb{F}_2^k \to \mathbb{F}_2^{n-k}$ . To prove the injectivity of a linear function, we refer to Lemma 1.

**Lemma 1.** A linear function C is injective iff it holds that  $C(X) = \{0\}^n \implies X = \{0\}^k$ .

When transmitting a codeword  $Y \in \mathbf{C}$  over an unreliable communication channel, the receiver can obtain a faulty codeword  $\tilde{Y} = \langle X \oplus E | X' \oplus E' \rangle$ , where  $\langle E | E' \rangle$  is the *error vector* that affected the transmission. The number of faults to correct within a single codeword depends on the code's *minimum distance*  $\delta$ . Therefore, we denote an [n,k]-code satisfying a minimum distance of  $\delta$  as  $[n,k,\delta]$ -code.

**Definition 13** (Minimum Distance). The minimum distance  $\delta$  of an [n,k]-code  $\mathbf{C}$  is defined as  $\min_{\forall Y,Z \in \mathbf{C},Y \neq Z} \mathsf{HD}(Y,Z) = \min_{\forall Y,Z \in \mathbf{C},Y \neq Z} \mathsf{HW}(Y \oplus Z) = \min_{\forall Y \in \mathbf{C}} \mathsf{HW}(Y)$ .

In the above definition,  $\mathsf{HD}(Y,Z)$  denotes the Hamming Distance (HD) of two different codewords Y and Z, i.e. the number bits which differ between Y and Z, while  $\mathsf{HW}(.)$  denotes the Hamming Weight (HW) of a codeword.

To correct the faults,  $\tilde{Y}$  is replaced by its nearest valid codeword, i.e. the codeword with minimal distance to  $\tilde{Y}$ . Accordingly,  $\tilde{Y}$  will only be correctly replaced by Y if the distance between Y and  $\tilde{Y}$  is still smaller than the distance between  $\tilde{Y}$  and other codewords. This directly leads to Lemma 2. Hence, an  $[n,k,\delta]$ -code can correct at most  $f=\frac{\delta}{2}-1$  faulty bits in a single codeword.

**Lemma 2.** An  $[n, k, \delta]$ -code can correct all faulty codewords  $\tilde{Y} = \langle X \oplus E | X' \oplus E' \rangle$  with  $\mathsf{HW}(E) + \mathsf{HW}(E') < \frac{\delta}{2}$ .

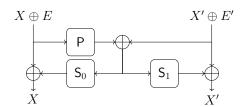

The translation from a faulty codeword to its nearest valid codeword can be done by means of syndrome decoding. For a valid codeword  $Y = \langle X|X'\rangle$  it holds that  $X' = X \cdot \underline{P}$  and therefore  $X' \oplus X \cdot \underline{P} = 0$ . For a faulty codeword  $\tilde{Y} = \langle X \oplus E|X' \oplus E'\rangle$  with the error vector  $\langle E|E'\rangle$ , we denote  $(X' \oplus E') \oplus (X \oplus E) \cdot \underline{P} = E' \oplus E \cdot \underline{P}$  as a syndrome. Once the syndrome is calculated, the Syndrome Decoder (SD) compares it to a pre-calculated lookup table of syndromes and their corresponding error vectors  $S : E' \oplus E \cdot P \mapsto \langle E|E'\rangle$ . If the syndrome matches one of the entries in the table, it means that an error has occurred and the decoder can use the associated error vector to correct the error. Based on syndrome decoding, we can correct faulty codewords as shown in Figure 2. We call the place where such a correction is made a correction point.

We remark that S is split into two functions namely  $S_0: E' \oplus E \cdot \underline{P} \mapsto E$  and  $S_1: E' \oplus E \cdot \underline{P} \mapsto E'$ , meaning that both receive the syndrome. Syndrome decoders  $S_0$  and  $S_1$  predict E and E' correctly as long as the fault can be corrected by the underlying C. Hence, it must hold that  $HW(E) + HW(E') < \frac{\delta}{2}$  to correct  $\tilde{Y}$  with an  $[n, k, \delta]$ -code C.

#### 2.4.2 Majority Voting

A simple yet effective correction point derived from an  $[n,1,\delta]$ -code with  $C:\mathbb{F}_2\mapsto\mathbb{F}_2^n$  and  $C(x) = \{x\}^n$  can correct up to  $f = \frac{\delta}{2} - 1$  faults in a codeword with an odd codeword size of  $n = \delta$  through the application of a technique known as Majority Voting (MV). In essence, MV involves examining each bit within the codeword and identifying the majority value among them. By aligning the bits with the majority decision, the correction point effectively corrects up to f faults in the codeword. Typically, the correction points are designed to receive the redundantly generated results of a system, which often involves obtaining the same output from n independent and parallel instances. For example, consider a scenario where three cipher cores simultaneously process identical inputs. In this setup, the correction points are responsible for evaluating these redundant outputs in order to correct one fault per output bit. Since the independent instances operate without sharing any signals, the occurrence of a fault in one instance does not impact the outputs of the other instances. Additionally, given that each output bit is corrected individually, there is no necessity for the instances to adhere to the independence property which reduces the area overhead associated with MV to a factor of n due to the presence of these n parallel instances plus an additional MV circuit. If the correction is applied exclusively to the system's output, the effectiveness of MV is constrained as it can only correct a total of f faults throughout the entire execution of the system, as opposed to f faults per clock cycle. Consequently, to attain the desired level of fault security denoted as  $(f, \tau_{bf}, mc_{\infty})$ , the correction logic must be capable of addressing the cumulative sum of faults that an adversary could potentially inject during the system's execution. This necessitates correcting a much larger number of faults, rendering the corresponding overhead arising from redundancy impractical for our needs.

#### 2.4.3 Impeccable Circuits

Aghaie et al. apply the aforementioned  $[n,k,\delta]$ -codes in Concurrent Error Detection (CED) schemes for hardware circuits  $[\mathrm{AMR}^+20]$ . The presented strategy allows to limit the fault propagation in a way that the circuit guarantees the detection of up to f faults at arbitrary positions when employing an  $[n,k,\delta]$ -code. Again f refers to the number of simultaneously injected faults as introduced in Section 2.3.3 and applied in Definition 10. As detection of faults is not enough to prevent SIFA, a follow-up work shows a scheme for correcting faults at arbitrary positions by applying an  $[n,k,\delta]$ -code [SRM20]. To implement the error correction scheme, we commence with a general sequential circuit, as illustrated in Figure 1. To simplify matters, we assume  $|\mathbf{IN}| \mod k = 0 \land |\mathbf{FB}| \mod k = 0$  meaning that the input state of the round function and the feedback state are both multiples of k bits. In accordance with the  $[n,k,\delta]$ -code, each k-bit message X, carried by a dedicated k-bit segment of  $\mathbf{IN}$  or  $\mathbf{FB}$ , can be encoded into its respective codeword  $Y = \langle X|X'\rangle$  by applying the parity mapping function P, as defined in Section 2.4.1. For example, if  $|\mathbf{IN}| = q \cdot k$  (or  $|\mathbf{FB}| = q \cdot k$ ), we define  $\mathsf{F} : \mathbb{F}_2^{q \cdot k} \mapsto \mathbb{F}_2^{q \cdot (n-k)}$ . This function maps a collection of q messages, each composed of k bits, to their corresponding q parities, each comprised of n-k bits.

**Figure 2:** Correction point correcting a faulty codeword  $\langle X \oplus E | X' \oplus E' \rangle$  back to  $\langle X | X' \rangle$ .

Figure 3: CED based on Impeccable Circuits II with injective F.

Specifically, F applies P individually to each of the q messages. While the straightforward procedure mentioned above applies to data signals, it is essential to carefully consider control signals, which are typically processed by a finite-state machine and play a critical role in the round function. Changes in the control flow can potentially enable an adversary to propagate intermediate states to the output. To prevent any alterations in the control flow, every control signal in **IN** must be encoded separately, distinct from the data signals or other control signals [SRM20]. In practical terms, this means that each single-bit control signal is padded with zeros to create an individual k-bit chunk while data signals are only padded if the whole state encompasses no multiple of k bits.

Further, we assume that F is an injective function<sup>4</sup>. Therefore, the redundancy size must be at least as large as the message size, implying that  $n \geq 2k$ . Additionally, since F is an injective function, the redundant counterpart of the round function R can exclusively operate on the parities of the input signals. This results in a redundant round function denoted as  $R' = F \circ R \circ F^{-1}$ , operating on the set of parities belonging to the input signals of the round function. In particular, we denote the set of wires driving the redundancy state of the feedback signals as FB'. To construct a full correction point for FB we employ the same principle as for defining F to establish  $SD_0 : \mathbb{F}_2^{q \cdot (n-k)} \mapsto \mathbb{F}_2^{q \cdot k}$  (and  $SD_1 : \mathbb{F}_2^{q \cdot (n-k)} \mapsto \mathbb{F}_2^{q \cdot (n-k)}$ ). These functions are responsible for decoding the syndromes of q parity chunks. As a result, we can apply q correction points in parallel to correct the input state of the round function. Figure 3 shows the schematic of the circuit from Figure 1 after the application of such a CED.

It is important to note that contrary to MV as explained in Section 2.4.2, the round functions R and R', together with the correction logic, must be implemented in a way that the propagation of a single intermediate fault to multiple faults within  $\mathbf{ST}$  or  $\mathbf{ST}'$  is prevented. This necessitates their implementation in a manner that ensures the independence property. In the case of an ECC with  $\delta = 2f + 1$ , the output of  $\mathsf{SD}_0$  remains unchanged even when up to f faults are introduced at its input. It means that  $\mathsf{SD}_0$  does not propagate any fault E with  $\mathsf{HW}(E) < f$ . Therefore, it is feasible to instantiate F and the corresponding XOR operation separately. However, this does not hold true for  $\mathsf{SD}_1$  [SRM20]. Consequently, all sub-circuits enclosed by dashed red lines in Figure 3 must adhere to the independence property. Unfortunately, this may lead to the necessity of incorporating multiple instances of the same correction logic, potentially increasing the area requirements. To mitigate the increase in area overhead, the authors of [SRM20] suggested the insertion of multiple correction points while maintaining the circuit's latency, provided that the round function R can be decomposed. Specifically, they suggest to split

$<sup>^4</sup>$ Indeed, another scheme based on non-injective F is also presented in [SRM20]. However, according to the results presented in [BBM $^+$ 22], we excluded such cases in this work.

R into two sub-functions  $R = R_1 \circ R_0$  in a way that  $R_1$  becomes linear. Further, if  $R_1$  can be effectively represented as a binary matrix composed of elements from the finite field  $\mathbb{F}_2^k$ , it has been established in  $[AMR^+20]$  that  $R_1$  exhibits a property of fault non-propagation. Consequently, when implemented in accordance with the aforementioned decomposition, there is no necessity for an additional correction point before the computation of R<sub>1</sub>. However, if R<sub>0</sub> and R<sub>1</sub> are both non-linear, this would necessitate additional circuitry to implement multiple correction points. In this case, two individual correction points are required to correct the inputs of  $R_0$  and  $R_1$  respectively. It is worth noting that the round function can be decomposed into multiple sub-functions, as opposed to having just one linear and one non-linear sub-function. An extreme example of this approach is illustrated in [BKHL20], where a correction point is introduced for each non-linear gate. While this strategy simplifies the achievement of the independence property, it is important to consider that the substantial increase in the number of correction points could potentially result in an impractical area overhead, depending on the specific target. Since we allow an adversary to introduce up to f faults per clock cycle, it is important to note that the number of faults to be corrected between two correction points is effectively doubled, as observed in [SRM20]. To illustrate this, consider an adversary with the capability to inject a single fault per clock cycle. Exemplary, the adversary can fault the input of a specific register in one clock cycle and fault the output of another register in the subsequent clock cycle. In this scenario, the fault introduced at the register's input is propagated to its output, resulting in two simultaneous faults on register outputs. Consequently, the underlying ECC must be designed to correct for a total of 2f faults to achieve  $(f, \tau_{bf}, mc_{\infty})$ -fault security.

### 3 Technique

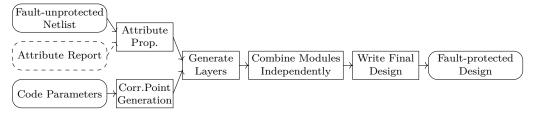

In this section, we present AGEFA's procedure (cf. Figure 4) for converting an unprotected implementation into a fault-resistant design, utilizing the technique outlined in Impeccable Circuits II [SRM20]. We have chosen to adopt the scheme due to its assurance of security within our designated fault adversary model, a feat that, practically, cannot be achieved through the application of, for instance, cipher-level MV. Additionally, Impeccable Circuits II provides a high degree of flexibility in its implementation, primarily through the ability to decompose the round function as needed. This flexibility permits us to optimize protection in two vital dimensions: latency and area. On one hand, we can opt for no decomposition to minimize the latency, while on the other hand, we have the option to decompose the round function into multiple sub-functions to reduce the overall area footprint at the cost of higher latency. Moreover, this flexibility allows us to experiment with various configurations, enabling us to identify the most suitable one. This advantage is a direct result of automation and would be unattainable through manual methods.

**Figure 4:** Procedure of AGEFA to protect a circuit against FI attacks.

AGEFA follows the process outlined in Figure 4. The process begins with receiving a gate-level netlist written in Verilog. The given netlist implements no protection against FI attacks but can be a masked implementation to be protected against SCA. To prepare

the netlist to be processed by AGEFA, the designer must first synthesize the behaviorallevel description of the design using a synthesizer such as Design Compiler (DC) [Inc] or Yosys [Wol]. Additionally, for every primary input or output wire w, the designer has to set attribute(w) through textual annotations in the netlist in the following manner:

- If wire w should be identified as the clock signal, it must hold that  $\mathtt{attribute}(w) = \mathtt{clock}$ . In this work, we denote the clock signal as  $\mathtt{clk}$ .

- If wire w should be identified as the reset signal, it must hold that  $\mathsf{attribute}(w) = \mathsf{reset}$ . In this work, we denote the reset signal as  $\mathsf{rst}$ .

- For every primary input or output wire w which carries a data signal (including plaintext, ciphertext, and key), it must hold that attribute(w) = secure. Likewise, if w carries a control signal, e.g. enable or done signals, it must hold that attribute(w) = control. Further, for every primary input wire (resp. output wire) w, it holds that w ∈ IN (resp. w ∈ OUT) iff attribute(w) = secure ∨ attribute(w) = control.

- If we assume that  $R = R_{h-1} \circ \dots R_0$ , i.e. if the round function is a decomposition of h sub-functions, and we abstract every sub-function with a module  $\mathcal{R}_{h-1}, \dots, \mathcal{R}_0$ , it holds that  $\mathtt{attribute}(w) = \mathtt{layer}$  for every intermediate wire w with  $w \in \mathbf{IN}_{\mathcal{R}_i} \land w \in \mathbf{OUT}_{\mathcal{R}_{i-1}} \land 0 < i \leq h$ .

Once the annotated netlist is received, AGEFA applies a slightly modified version of the AGEMA's parser, resulting in a graph  $(\mathbf{G}, \mathbf{W})$  that represents the netlist based on the circuit model described in Section 2.2. We straightforwardly render R into a separate set of modules  $\mathbf{R}$ . Again,  $\mathcal{R} \in \mathbf{R}$  abstracts one coordinate function of R. If R is decomposed, we create additional coordinate functions for every intermediate wire x with  $\mathsf{attribute}(x) = \mathsf{layer}$ . More concretely, if  $\mathsf{attribute}(x) = \mathsf{layer}$ , we add a new module  $\mathcal{X}$  to  $\mathbf{R}$  while  $\mathsf{OUT}_{\mathcal{X}} = \{x\}$  and  $\mathsf{IN}_{\mathcal{X}}$  can contain primary input wires or other intermediate wires w with  $\mathsf{attribute}(w) = \mathsf{layer}$ . Further, we render the register stage into another set of modules  $\mathsf{FF}$  while  $\mathcal{FF} \in \mathsf{FF}$  abstracts a single register. Based on this representation of the circuit, AGEFA performs the following high-level steps.

- To generate a secure and efficient design, AGEFA sets all parameters mentioned in Table 2 for every signal of the circuit.

- Based on the given message size k and fault cardinality 2f, AGEFA automatically finds an efficient ECC including all operations required to construct a correction point. For every operation required for the correction, AGEFA generates a module that satisfies the independence property.

- AGEFA transforms all coordinate functions of the (decomposed) combinational logic in a way that they fulfill the independence property.

- Subsequently, it proceeds to construct the three functions, as indicated by the dashed red lines in Figure 3. In this process, AGEFA connects the generated functions, each of which independently satisfies the independence property. Importantly, the compositions are crucially designed to uphold the independence property.

- Lastly, AGEFA finalizes the protected design by connecting the cascaded functions.

#### 3.1 Attribute Propagation

We repeat that the protection mechanism presented in Impeccable Circuits II [SRM20] takes special care of the Finite State Machine (FSM) as injecting faults on the FSM may change the control flow, i.e. enables an adversary to observe intermediate states

of the design. Therefore, AGEFA must distinguish between the protection of control signals and data signals. While all  $w \in \mathbf{IN}$  are already annotated, AGEFA automatically determines all  $\mathsf{attribute}(x)$  for every  $x \in \mathbf{ST}$  and for every  $x \in \mathbf{FB}$  (see Figure 1). To propagate the attributes of the primary inputs through the circuit, we can apply Algorithm 1 of [KMMS22] on  $\mathbf{R}$  and  $\mathbf{FF}$ . Hence, the following two rules apply.

- For every  $\mathcal{R} \in \mathbf{R}$ , it holds for the output wire  $w \in \mathbf{OUT}_{\mathcal{R}}$  that  $\mathsf{attribute}(w) = \mathsf{control}$  if  $\nexists x \in \mathbf{IN}_{\mathcal{R}}$ :  $\mathsf{attribute}(x) = \mathsf{secure}$ . Conversely,  $\mathsf{attribute}(w) = \mathsf{secure}$  if  $\exists x \in \mathbf{IN}_{\mathcal{R}}$ :  $\mathsf{attribute}(x) = \mathsf{secure}$ .

- For every  $\mathcal{FF} \in \mathbf{FF}$ , it holds for the output wire  $w \in \mathbf{OUT}_{\mathcal{FF}}$  that  $\mathtt{attribute}(w) = \mathtt{attribute}(x)$  if  $x \in \mathbf{IN}_{\mathcal{FF}}$  denotes the input wire with  $\mathtt{attribute}(x) \neq \mathtt{clock}$ .

If AGEFA processes a masked design operating on multiple shares, we make sure that the error-correction logic does not violate the SCA-security assumptions of the original design. Specifically, if a masked design adheres to probing security (resp. composability) under the robust probing model, the final masked and fault-tolerant design must similarly guarantee probing security (resp. composability) under the same model. Implementing the error-correction logic SCA-securely can be done share-wise, allowing each share domain to be processed independently, thereby satisfying the PINI-notion. However, it is crucial to ensure that the error-correction logic does not mistakenly combine shares from different domains. To avoid this, each message (for encoding) must only contain shares from the same share domain, which can be achieved by labeling every  $w \in \mathbf{ST}$  with a corresponding share domain, i.e.  $share\_domain(w)$ . The designer has to provide an additional report assigning all  $w \in \mathbf{ST}$  that carry shared variables to their corresponding share domain share  $domain(w)^5$ . If a handcrafted masked implementation is given to AGEFA, the designer must manually generate and provide the wires with their respective share domain, i.e. in the synthesis script or the behavioral design, which might be a challenging task. On the other hand, if the design is entirely made by secure and composable gadgets, such as a result of AGEMA, we can annotate the required wires in each gadget separately and propagate the annotation during the synthesis procedure<sup>6</sup>. However, if share domain(w)for a  $w \in \mathbf{ST}$  is not specified in the report, e.g. in case of  $\mathsf{attribute}(w) = \mathsf{control}$ , we set share domain(w) = 0 while it holds that share domain(w) > 0 for all w carrying a shared variable. This annotation ensures that subsequent stages, such as Algorithm 5, encode signals exclusively from the same share domain within a given message. We acknowledge that annotating a masked circuit in this manner can be a tedious task. Nonetheless, if we were to limit the annotation to only primary inputs of the circuit, we would need to exercise greater caution when consolidating signals into the same share domain. This cautious approach would, in turn, lead to a further increase in the area overhead of the final result.

#### 3.1.1 Optimizations

If the round function R can be expressed as the composition of two sub-functions,  $R = R_1 \circ R_0$ , and  $R_1$  can be represented as a binary matrix with elements in  $\mathbb{F}_2^k$ , there is no need to correct the inputs of  $R_1$  [AMR<sup>+</sup>20, SRM20]. Hence, avoiding an additional correction point leads to a more efficient design w.r.t circuit size and latency. Therefore, AGEFA searches in the module-based representation of R, denoted as  $\mathbf{R}$  for a subset of modules  $\mathbf{R}_1 \subset \mathbf{R}$

$<sup>^5\</sup>mathrm{The}$  report\_attribute command ensures that Synopsys DC creates such a report.

<sup>&</sup>lt;sup>6</sup>Technically, Yosys automatically propagates all user-defined attributes in the RTL code to the netlist, unless the -noattr flag is set. For Synopsys DC, the designer must define an attribute for each gadget type through define\_user\_attribute and propagate it via propagate\_user\_attributes command. This procedure results in a separate attribute report that contains all nets with their corresponding attribute, which then can be given to AGEFA.

end if

end if

end for  $\mathbf{X} \leftarrow \mathbf{X} \setminus \{x\}$

14:

15:

16:

17:

18:

19: 20:

21:

22: end for

Algorithm 1 Mark inputs of linear functions

$X \leftarrow X \cup OUT_{\mathcal{R}}$

$\mathbf{Y} \leftarrow \mathbf{Y} \cup \mathbf{OUT}_{\mathcal{R}}$

where the instructions can be represented as the aforementioned matrix multiplication. This procedure is twofold. First, AGEFA extracts all  $\mathcal{R} \in \mathbf{R}$  representing linear functions. Then, AGEFA considers all linear  $\mathcal{R} \in \mathbf{R}$  as a linear layer and checks if the correction at inputs can be safely removed.

```

Input: R

▶ The module-based abstractions of the round function.

Input: FF

▶ The module-based abstraction of the register stage.

Input: IN

▶ The set of wires carrying primary input signals

Output: R

▶ The round function with marked input and output wires.

1: \mathbf{R}_0 \leftarrow \{ \mathcal{R} \in \mathbf{R} | \exists w \in \mathbf{OUT}_{\mathcal{R}} : \mathtt{linear} \ \mathtt{index}(w) = 0 \}

2: \mathbf{R}_1 \leftarrow \mathbf{R} \backslash \mathbf{R}_0

3: \mathbf{X} \leftarrow \emptyset

4: for \forall \mathcal{R} \in \mathbf{R}_0 do

X \leftarrow X \cup OUT_{\mathcal{R}_0}

6: end for

\mathbf{Y} \leftarrow \mathbf{X}

for \forall x \in \mathbf{X} do \triangleright Check if the non-linear output is an input of only linear functions.

\mathbf{Z} \leftarrow \{\mathbf{OUT}_{\mathcal{F}\mathcal{F}} | \mathcal{F}\mathcal{F} \in \mathbf{FF} : x \in \mathbf{IN}_{\mathcal{F}\mathcal{F}} \}

▷ Get the register output wire.

if \nexists z \in IN_{\mathcal{R}} | \mathcal{R} \in \mathbf{R}_0 : z \in \mathbf{Z} then

10:

for \forall z \in \mathbf{Z} do \triangleright Mark register outputs that are no inputs of linear functions.

11:

linear index(z) \leftarrow 1

12:

13:

end for

```

for  $\forall \mathcal{R} \in \mathbf{R}_1$  do  $\triangleright$  Consider linear layer outputs as inputs of another linear layer.

if  $\nexists w \in \mathbf{IN}_{\mathcal{R}}$ : linear\_index $(w) = 0 \land w \notin \mathbf{IN} \land w \notin \mathbf{Y}$  then

To identify every  $\mathcal{R} \in \mathbf{R}$  representing a linear function, we create its Algebraic Normal Forms (ANFs) based on  $INST_{\mathcal{R}}$  and examine whether it exclusively comprises monomials with an algebraic degree of one. If R is confirmed to be abstract a linear function, we mark  $w \in \mathbf{OUT}_{\mathcal{R}}$  by setting linear  $\mathrm{index}(w) = 1$ . Otherwise, we set linear index(w) = 0. Additionally, it has been demonstrated in [AMR<sup>+</sup>20] that the outputs of a multiplexer stage controlled by rst can be directly integrated into the following linear layer without an additional correction. Thus, we set linear index(w) = 1 not only when  $\mathcal{R}$  abstracts a linear function but also in cases where  $\mathcal{R}$  represents a function with non-linear components limited to multiplexers using rst as the select signal. Hence, it holds that linear index(w) = 1 if the ANF of  $\mathcal{R}$  exclusively contains monomials with an algebraic degree of one or monomials with an algebraic degree of two with rst as one of the variables. This approach enables the identification of such multiplexers, even if they are not explicitly represented by dedicated multiplexer modules in the netlist but are expressed in their underlying algebraic form. After this step, the output wire w of every  $\mathcal{R} \in \mathbf{R}$  is either marked as linear (linear\_index(w) = 1) or non-linear (linear\_index(w) = 0) and we denote the list of linear modules as  $\mathbf{R}_1 = \{ \mathcal{R} \in \mathbf{R} | \exists w \in \mathbf{OUT}_{\mathcal{R}} : \mathtt{linear\_index}(w) = 1 \}$ . Similarly, we denote the non-linear modules as  $\mathbf{R}_0 = \mathbf{R} \setminus \mathbf{R}_1$ . To identify if  $\mathbf{R}_1$  abstracts one or multiple layer(s) which do not require additional correction, we apply Algorithm 1. Initially, in Lines 3-7, Algorithm 1 creates two sets, X and Y, encompassing all output

wires of  $\mathbf{R}_0$ . In the following Lines 9-14, Algorithm 1 systematically examines each output wire  $x \in \mathbf{X}$  produced by a non-linear function, determining whether its signal is exclusively propagated (though a register, as checked in Line 9) to the inputs of linear coordinate functions. This criterion is satisfied iff the signal carried by x is not propagated to the input of any  $\mathcal{R} \in \mathbf{R}_0$ . To identify such wires, Algorithm 1 marks every input wire of  $\mathbf{R}_1$ , denoted as z in Line 12, meeting this condition by setting linear index(z) = 1. Additionally, in Lines 15-20 the algorithm considers all output wires of linear functions and assesses whether their signals are exclusively propagated to the inputs of other linear coordinate functions. This step enables the detection of multiple cascaded linear layers. Ultimately, all elements  $\mathcal{R} \in \mathbf{R}$  possessing solely linear inputs and outputs are identified as constituting a linear layer. Formally, we denote the linear layer as  $\mathbf{L} = \{ \mathcal{R} \in \mathbf{R} | \nexists w \in \mathbf{OUT}_{\mathcal{R}} \cup \mathbf{IN}_{\mathcal{R}} : \mathtt{linear\_index}(w) = 0 \}$  with a joint set of primary input wires  $IN_L$  and primary output wires  $OUT_L$ . We remark, that both sets  $IN_L$ and  $\mathbf{OUT_L}$  must be sorted based on the signal names. Utilizing the information from  $L, IN_L, and OUT_L, the procedure presented in Algorithm 2 determines whether the$ correction point can be removed from all wires in  $IN_{L}$ . Specifically, it examines if the implementation of L can be represented as a binary matrix with elements in  $\mathbb{F}_2^k$ . A crucial condition for such a representation is that both  $|IN_L|$  and  $|OUT_L|$  are multiples of k, except rst, which is encoded into a separate message. Consequently, rst within  $|IN_L|$  is counted as k signals. If L satisfies this condition, indicating that  $|IN_L|$  and  $|OUT_L|$  are multiples of k, Algorithm 2 is executed. Otherwise, we set linear index(w) = 0 for all  $w \in \mathbf{IN_L} \cup \mathbf{OUT_L}$ .

In Lines 2-9 of Algorithm 2, each k-bit message derived from the sorted primary wires of  $\mathbf L$  is assigned a distinct linear index greater than 0. This annotation signifies that no correction is necessary. However, Algorithm 2 is responsible for verifying whether the conditions for removing the correction are indeed met. If not, Algorithm 2 resets all linear indices to 0 (cf. Lines 15 and 20). This reset implies that correction is required for all signals. To assess this, AGEFA iterates through all chunks consisting of k modules and stores both their inputs and linear indices. Two conditions must be satisfied to warrant the removal of the correction point.

- 1. The same input signal (except the signal carried by rst) must not be distributed across multiple coordinate functions forming a k-bit message. This condition is examined in Line 13.

- 2. Each coordinate function forming a k-bit message should receive the same number of inputs with identical linear indices. This condition is examined in Line 18.

It is important to note that the question whether the correction logic can be removed or not depends on the order of the wires in  $\mathbf{IN_L}$  and  $\mathbf{OUT_L}$ . We specifically examine only the case where  $\mathbf{IN_L}$  and  $\mathbf{OUT_L}$  are sorted based on the wire names while also unsorted  $\mathbf{IN_L}$  and  $\mathbf{OUT_L}$  can lead to a removed correction point. However, validating all these diverse orderings is computationally infeasible. Instead, we choose this sorted representation based on the belief that it is likely to be implemented, given that it results in a k-bit message for k subsequent bits of a larger state. To illustrate, in the context of a cipher with a 64-bit round state  $\{x_0,\ldots,x_{63}\}$ , and k=4, we assume that a matrix representation in  $\mathbb{F}_2^4$  is implemented by considering sets such as  $\langle x_0,x_1,x_2,x_3\rangle,\ldots,\langle x_{60},x_{61},x_{62},x_{63}\rangle$  as 4-bit messages. In other words, we assume that a designer would interpret the 64-bit state as 16 subsequent 4-bit words. However, if the designer chooses another representation, AGEFA cannot remove the correction point resulting in a design that is still secure but not as efficient as possible.

#### Algorithm 2 Remove the correction point

```

Input: L

▷ The sorted linear layer with marked linear outputs

Input: IN_L, OUT_L

\triangleright A sorted list of input and output wires of L

Input: k

▶ The message size

▶ The linear layer with updated linear outputs and inputs

Output: L

1: q \leftarrow 0

2: for \forall w \in \mathbf{IN_L} \ \mathbf{do}

linear_index(w) \leftarrow \left| \frac{q}{k} \right| + 1

3:

q \leftarrow q + 1

4:

5: end for

6: for \forall w \in \mathbf{OUT_L} do

7:

linear_index(w) \leftarrow \lfloor \frac{q}{k} \rfloor + 1

8:

q \leftarrow q + 1

9: end for

10: for \forall q \in \{0, k, 2k, \dots, |\mathbf{OUT_L}| - k\} do

\mathbf{M} \leftarrow \{\mathcal{L}_q, \dots, \mathcal{L}_{q+k-1}\} \subset \mathbf{L}

\mathbf{for}\ \forall (\mathcal{M},\mathcal{M}^*) \in \mathbf{M} \times \mathbf{M}: \mathcal{M} \neq \mathcal{M}^*\ \mathbf{do}

12:

\mathbf{if}\ \exists w \in \mathbf{IN}_{\mathcal{M}} \cap \mathbf{IN}_{\mathcal{M}^*} : \mathtt{attribute}(w) \neq \mathtt{reset}\ \mathbf{then}

13:

for \forall w \in \mathbf{IN_L} \cup \mathbf{OUT_L} do

14:

linear\_index(w) \leftarrow 0

15:

end for

16:

17:

end if

if |\mathbf{IN}_{\mathcal{M}}| \neq |\mathbf{IN}_{\mathcal{M}^*}| \vee (\exists w \in \mathbf{IN}_{\mathcal{M}} \wedge \nexists q \in \mathbf{IN}_{\mathcal{M}^*} : \mathtt{linear\_index}(w) =

18:

linear index(q)) then

for \forall w \in \mathbf{IN_L} \cup \mathbf{OUT_L} do

19:

linear\_index(w) \leftarrow 0

20:

21:

end for

end if

22:

end for

23:

24: end for

```

#### 3.2 Correction Point Generation

The designer specifies the code parameters, i.e. the message size k and the maximum number of faults to correct within one clock cycle, usually set to 2f to achieve  $(f, \tau_{bf}, mc_{\infty})$ -fault security. Utilizing these parameters, AGEFA estimates the appropriate ECC parameters  $[n, k, \delta]$ . As outlined in Lemma 2 and Section 2.4.3, it holds that  $n \geq 2k$ . Further, the underlying ECC must correct 2f faults, hence  $\delta = 4f + 1$ .

#### 3.2.1 Error-Correcting Code (ECC) Generation

The procedure for finding a binary, linear, systematic, and injective  $[n, k, \delta]$ -code, denoted as  $\mathbb{C}$  which is a vector subspace of  $\mathbb{F}_2^n$  is outlined in Algorithm 3. It processes every message X by assigning a parity X' and generating the codeword  $Y = \langle X|X'\rangle$ . In Line 5, it is checked if Y can be added to  $\mathbb{C}$  without violating the code's minimum distance and injectivity, i.e. by checking if the minimum distance of Y and all other codewords of  $\mathbb{C}$  is sufficient and by ensuring that no other codeword in  $\mathbb{C}$  shares X' as parity. As long as Y is not a suited codeword for  $\mathbb{C}$ , we increment its parity X' until the codeword satisfies all the requirements. Algorithm 3 repeats this procedure until all  $X \in \mathbb{F}_2^k$  are associated with a corresponding X' in  $\mathbb{C}$ . The presented procedure follows a Greedy approach for constructing a, so-called, lexicographic code [CS86, Con90]. We remark that (1) such a code exists for all possible k and d [BP93], (2) the resulting codes are provably linear,

**Algorithm 3** Generation of a binary, linear, systematic, and injective  $[n, k, \delta]$ -code.

```

Input: k, \delta

\triangleright Message size k and minimum distance \delta

Output: C

\triangleright A binary, linear, systematic, and injective [n, k, d]-code

1: \mathbf{C} \leftarrow \emptyset

2: for X = 0 to 2^k - 1 do

▶ Iterate through all possible messages

X' \leftarrow 0

\triangleright X' stores the parity of X

Y \leftarrow \langle X|X'\rangle

4:

while \exists Z : \langle T|T' \rangle \in \mathbf{C} s.t. \mathsf{HD}(Y,Z) < \delta \lor X' = T' do

\triangleright Check codeword Y

5:

X' \leftarrow X' + 1

6:

Y \leftarrow \langle X|X'\rangle

7:

8:

end while

\mathbf{C} \leftarrow \mathbf{C} \cup \{Y\}

▶ Add the new codeword to the code

9:

10: end for

```

systematic, and injective [Lev60, CS86, BP93], and (3) n is usually minimal [CS86]. The injectivity and systematicity of the code generated by Algorithm 3 are easily provable due to the algorithm's nature. However, the linearity of the code is not immediately apparent. A lexicographic code, where the codewords are arranged and iterated in lexicographic order, was first proven to be linear by Levenshtein [Lev60]. Brualdi et al. later generalized this proof to lexicographic codes generated using arbitrarily ordered bases of  $\mathbb{F}_2^n$ , resulting in a lexicographic ordering on the coefficient vectors [BP93]. As Algorithm 3 iterates through the codewords in lexicographic order, the generated codes are also linear by extension of the aforementioned proofs. In summary, Algorithm 3 leads to codes with small parities and thus an efficient encoding. However, the designer is free to force AGEFA to employ a certain ECC that better fits particular needs. From  $\mathbb{C}$ , we derive the mapping  $\mathbb{P}: \mathbb{F}_2^k \to \mathbb{F}_2^{n-k}$  between messages  $X \in \mathbb{F}_2^k$  and their corresponding parities  $X' \in \mathbb{F}_2^{n-k}$  in form of a lookup table. We compute the table lookup for an arbitrary message X as  $X \cdot \underline{P} = X'$ . Further, we generate the mapping  $\mathbb{P}^{-1}(.)$ , again as a lookup table to map arbitrary parities back to their corresponding messages.

#### 3.2.2 Syndrome Decoder (SD) Generation

Algorithm 4 constructs the corresponding SD of the previously generated  $[n, k, \delta]$ -code  $\mathbb{C}$ . As shown in Figure 2, we split the SD into two separate functions, namely  $S_0 : E' \oplus E \cdot \underline{P} \mapsto E$  and  $S_1 : E' \oplus E \cdot \underline{P} \mapsto E'$ . As previously mentioned, we generate the mappings  $S_0$  and  $S_1$  as lookup tables. Algorithm 4 generates mappings for all possible error vectors that  $\mathbb{C}$  can correct, specifically for error vectors with less than  $\frac{\delta-1}{2}$  faulty bits. In Line 3, the syndrome is computed based on the error vector. The syndrome is subsequently mapped to the corresponding parts of the error vector and stored as a mapping (lookup table) in  $S_0$  and  $S_1$ . These lookup tables are not complete, meaning that  $S_0$  and  $S_1$  do not cover all  $\langle E|E'\rangle \in \mathbb{F}_2^n$ . We deal with such cases in the following section.

#### 3.2.3 Algebraic Representation

To integrate P,  $P^{-1}$ ,  $S_0$ , and  $S_1$  into a hardware design and to facilitate further steps, we convert the lookup tables into a set of modules in accordance with Definition 1. We repeat that a module can abstract complex operations consisting of multiple gates and inputs. For every module  $\mathcal{M}$  with  $|\mathbf{IN}_{\mathcal{M}}| = n$  inputs and  $|\mathbf{OUT}_{\mathcal{M}}| = m$  outputs, it holds that it can be formalized by an n-ary vectorial Boolean function with m coordinate functions. However, we can also decompose the Boolean functions in a way that multiple vectorial Boolean functions compute the module's intermediates in  $\mathbf{T}_{\mathcal{M}}$  while other functions process the intermediates to compute the primary outputs  $\mathbf{OUT}$ . We denote the resulting sets of

modules as  $\mathbf{P}$ ,  $\mathbf{P}^{-1}$ ,  $\mathbf{S}_0$ , and  $\mathbf{S}_1$  while every module in the set abstracts one coordinate function of the respective operation, e.g.  $\mathcal{P}_i$  denotes the *i*-th module in  $\mathbf{P}$  abstracting the *i*-th coordinate function of  $\mathbf{P}$ . Further, it holds that none of the modules stores intermediates, meaning that every module implements a Boolean function processing all input signals to compute a single output.

Since all functions are injective, their corresponding lookup tables may contain don't care values. For example,  $S_0$  and  $S_1$  certainly have such cases as explained above. To find the most efficient logic function that represents the lookup table even if it contains don't cares, we apply the Quine-McCluskey algorithm [Qui52, McC56] on every coordinate function of the respective mappings. Hence, every mapping is translated from a lookup table into its minimal sum-of-products form becoming efficient in terms of circuit size. Finally, we store the generated Boolean function, i.e. the minimal sum-of-products form, using a single instruction, in accordance with Definition 1, into the corresponding module.

#### 3.2.4 Optimizations

Depending on the complexity of the combinational logic, choosing  ${\bf C}$  with minimum n, as shown in Section 3.2.1 may not always be the optimal approach. As an example, consider an arbitrary linear, injective, and systematic [8, 4, 3]-code  ${\bf C}$  which is capable of correcting one fault in an 8-bit codeword with 4-bit message. It can be shown that it is possible to implement the mapping  ${\bf P}: \mathbb{F}_2^4 \to \mathbb{F}_2^4$ , where a message  $X: \langle x_3, x_2, x_1, x_0 \rangle$  is mapped to its corresponding parity  $X': \langle x_3', x_2', x_1', x_0' \rangle$ , using four separate coordinate functions  ${\bf p}_0, {\bf p}_1, {\bf p}_2, {\bf p}_3: \mathbb{F}_2^4 \to \mathbb{F}_2$  as follows.

$$x_3' = \mathsf{p}_3(x_3), \qquad x_2' = \mathsf{p}_2(x_2, x_1), \qquad x_1' = \mathsf{p}_1(x_2, x_0), \qquad x_0' = \mathsf{p}_0(x_3, x_2, x_1, x_0)$$

According to Figure 3 and the explanations given in Section 2.4.3, the redundant part of the round function, i.e. R', is derived as  $F \circ R \circ F^{-1}$ . We remark that each coordinate function of R' should satisfy the independence property. Therefore, the output of sub-functions of  $R \circ F^{-1}$  are the inputs of F, i.e. X in the above equations. Due to the independence property, coordinate functions  $p_0$  to  $p_3$  cannot share any inputs. As an example, the circuit which computes  $x_2$  must be instantiated three times as  $p_0$ ,  $p_1$ , and  $p_2$  receive  $x_2$ . In other words, each input of the coordinate functions  $p_0$  to  $p_3$  should be individually generated. This means that these coordinate functions need in total 9 individual inputs. As a side note, there is no other [8,4,3]-code with a smaller number of individual inputs.

If we, artificially, increase the parity size by one bit, we achieve a linear, injective, and systematic [9,4,3]-code with message-to-parity mapping  $Q: \mathbb{F}_2^4 \to \mathbb{F}_2^5$  which maps a message  $X: \langle x_3, x_2, x_1, x_0 \rangle$  to its corresponding parity  $X': \langle x_4', x_3', x_2', x_1', x_0' \rangle$  with the following five coordinate functions  $q_0, q_1, q_2, q_3, q_4: \mathbb{F}_2^4 \to \mathbb{F}_2$ .

$$x'_4 = \mathsf{q}_4(x_3), \quad x'_3 = \mathsf{q}_3(x_2), \quad x'_2 = \mathsf{q}_2(x_1), \quad x'_1 = \mathsf{q}_1(x_0), \quad x'_0 = \mathsf{q}_0(x_3, x_2, x_1, x_0)$$

Despite the larger parity size, the coordinate functions of Q need in total only 8 individual inputs. We remark that the number of individual inputs of P (resp. Q) has a

#### **Algorithm 4** Generation of the Syndrome Decoder (SD).

decisive influence on the complexity of the design, i.e. circuit size, as R' needs to employ these message-to-parity mappings. Consequently, a mapping with a minimal number of inputs per coordinate function can avoid multiple instances of the same combinational sub-circuit, potentially saving more area than that of the additional parity. The specific size of the circuit depends on the round function and the syndrome decoders, which generally become more complex as the parity size increases. Therefore, the designer has to balance between fewer instances of individual coordinate functions belonging to the round function and an increasingly complex SD.

To determine the optimal parity size, AGEFA automatically finds the parity size resulting in the smallest number of individual inputs for the message-to-parity mapping. This is done by incrementally increasing the parity size as long as the number of individual inputs decreases and continuing with the code that results in the smallest number of individual inputs. However, it is recommended to apply AGEFA on every design twice, once with these optimizations and once without, to ensure that the optimizations truly result in a decrease in the circuit size. If optimizing the parity size does not lead to a smaller circuit, it can be concluded that the SD becomes too complex and that the smallest possible parity size, i.e. AGEFA without optimizations, is a better choice.

#### 3.3 Layer Generation

In contrast to the round function, P,  $P^{-1}$ ,  $S_0$ , and  $S_1$ , are designed to process a single message (or parity) rather than the entire state ST. To correct ST, we have to decide which signals of ST can be securely corrected within a single message and which signals need to be processed separately. To address this limitation, we extend the modules to operate on ST, as given below.

#### 3.3.1 Generating Redundant State

To accurately encode every signal of the circuit state, it is necessary to construct the redundant counterpart belonging to  $\mathbf{ST}$ . Due to the importance of control signals, it holds that, every  $x \in \mathbf{ST}$  with  $\mathbf{attribute}(x) = \mathbf{control}$  builds its own message while k data signals can be processed within the same message. In particular, we pad every control signal x with k-1 leading zeros, resulting in an (n-k)-bit parity, denoted as  $X' = P(\langle \{0\}^{k-1}, x \rangle)$ . Contrary, data signals are encoded as k-bit chunks, each of which is denoted as  $X = \langle x_{k-1}, \ldots, x_0 \rangle$  and results in (n-k)-bit parity, derived as X' = P(X). X is only padded with i leading zeros if only k-i data signals are available, i.e. if the number of data signals is not a multiple of k bits. Furthermore, special care must be taken when the given design is masked since the combination of multiple share domains of the same variable within a k-bit message violates the security of masking. To transfer  $\mathbf{ST}$  into a padded state, denoted as  $\mathbf{SP}$ , we apply Algorithm 5.

Before executing Algorithm 5, we cluster the unpadded state  $\mathbf{ST}$  so that all signals with the same attribute, the same share domain, and the same linear index appear in groups one after the other while control signals make a distinct group. In Line 5 of Algorithm 5, a separate message is generated for each control signal by padding the message with (k-1) zeros. To indicate leading zeros, we insert dummy signals driving constant zero into  $\mathbf{SP}$  which we denote as  $0 \in \mathbf{SP}$  (see Line 5). As control signals are usually unmasked, and are associated to separate messages, their share domain can be neglected. In contrast, data signals (processed in Lines 7-16) cannot be combined in the same message if their share domains or linear indices are different. Therefore, we only combine data signals in a message with the same parameters and start a new message as soon as we reach a data signal with a different share domain or linear index. Finally, if the number of signals in a message is smaller than k, we fill the remaining space with zeros, see Line 19. Note that we process the feedback state  $\mathbf{FB}$  in the same way to receive a padded feedback state

#### **Algorithm 5** Secure padding of a state

```

Input: ST

▶ An unpadded but clustered state, i.e. a set of signals

Input: k

▶ The size of one message

Output: SP

▶ A padded state, i.e. a set of signals

1: q \leftarrow 0

2: l \leftarrow 0

3: for \forall w \in \mathbf{ST} \ \mathbf{do}

if attribute(w) = control then

4:

\mathbf{SP} \leftarrow \mathbf{SP} \cup \left\{ \left\langle \ \{0\}^{k-1}, w \right\rangle \right\}

5:

6:

if share\_domain(w) \neq q then

7:

\mathbf{SP} \leftarrow \mathbf{SP} \cup \{\langle \{0\}^{k-\overline{(|\mathbf{SP}| \mod k)}} \rangle\}

8:

q \leftarrow \mathtt{share\_domain}(w)

9:

else

10:

if linear_index(w) \neq l then

11:

\mathbf{SP} \leftarrow \mathbf{\overline{SP}} \cup \{\langle \{0\}^{k-(|\mathbf{SP}| \mod k)} \rangle\}

12:

q \leftarrow \mathtt{linear\_index}(w)

13:

end if

14:

end if

15:

\mathbf{SP} \leftarrow \mathbf{SP} \cup \{w\}

16:

end if

17:

18: end for

19: \mathbf{SP} \leftarrow \mathbf{SP} \cup \left\{ \left\langle \{0\}^{k - (|\mathbf{SP}| \mod k)} \right\rangle \right\}

```

**FP**. Further, we remark that **ST** and **FB** are clustered in the same way meaning that the signals of a certain register have the same index in both states. For example,  $u_i \in \mathbf{SP}$  denotes the input signal of the *i*-th register while  $v_i \in \mathbf{FP}$  denotes its corresponding output signal. Now, based on the padded data states **SP** and **FP**, we can create  $q \cdot (n-k)$  signals representing the corresponding parity states **SP**' and **FP**'.

#### 3.3.2 Extending ECC Modules

As depicted in Figure 3, **FB** must be given as an input state to the functions **F** of the correction logic while both **F** compute the parity state depending on **FB**. Here, we refer to the sets of outputs of the functions **F** as **U**' and **V**'. We highlight that both states indicate parity states as  $|\mathbf{U}'| = |\mathbf{V}'| = |\mathbf{FP}'|$  and that we derive the wire names of **U**' and **V**' from  $\mathbf{FP}'$  by extending every wire name of  $\mathbf{FP}'$  with an unique extension. Both functions  $\mathbf{F} : \mathbb{F}_2^{q \cdot k} \to \mathbb{F}_2^{q \cdot (n-k)}$  map  $\mathbf{FP}$  as a state of q concatenated k-bit messages to a state of q corresponding (n-k)-bit parities (**U**' and **V**'). This functionality is achieved through the parallel application of q instances of the modules in **P**, with each instance processing a single message. Therefore, we start with creating an additional set of modules  $\mathbf{F} = \{\mathcal{F}_0, \dots, \mathcal{F}_{q \cdot (n-k)-1}\}$  abstracting  $q \cdot (n-k)$  coordinate functions  $\mathbf{f}_i : \mathbb{F}_2^k \to \mathbb{F}_2$ . We remark that every  $\mathcal{F}_i \in \mathbf{F}$  computes exactly one signal of the parity state  $\mathbf{U}'$ . To instantiate every  $\mathcal{F}_i \in \mathbf{F}$  we apply Algorithm 6.